|                             | Embedded Syster | ns Lab Manual           |

|-----------------------------|-----------------|-------------------------|

| Ahmad Khayyat, Hazem Selmi, |                 | Saleh, Mansour Alharthi |

| Ahmad Khayyat, Hazem Selmi, |                 |                         |

| Ahmad Khayyat, Hazem Selmi, |                 | Saleh, Mansour Alharthi |

| Ahmad Khayyat, Hazem Selmi, |                 | Saleh, Mansour Alharthi |

| Ahmad Khayyat, Hazem Selmi, |                 | Saleh, Mansour Alharthi |

| Ahmad Khayyat, Hazem Selmi, |                 | Saleh, Mansour Alharthi |

| Ahmad Khayyat, Hazem Selmi, |                 | Saleh, Mansour Alharthi |

# **Table of Contents**

| 1. Experiment 1: Development Platform                | 1  |

|------------------------------------------------------|----|

| 1.1. Objectives                                      | 1  |

| 1.2. Parts List                                      | 1  |

| 1.3. Background                                      | 1  |

| 1.4. Tasks                                           | 8  |

| 1.5. Resources                                       | 9  |

| 1.6. Grading Sheet                                   | 10 |

| 2. Experiment 2: General-Purpose Input/Output (GPIO) | 10 |

| 2.1. Objectives                                      | 10 |

| 2.2. Parts List                                      | 10 |

| 2.3. Background                                      | 10 |

| 2.4. Tasks                                           | 14 |

| 2.5. Resources                                       | 15 |

| 2.6. Grading Sheet                                   | 15 |

| 3. Experiment 3: Interrupts                          | 15 |

| 3.1. Objectives                                      | 15 |

| 3.2. Parts List                                      | 15 |

| 3.3. Background                                      | 16 |

| 3.4. Tasks                                           | 23 |

| 3.5. Resources.                                      | 24 |

| 3.6. Grading Sheet                                   | 24 |

| 4. Experiment 4: Hardware Timers                     | 24 |

| 4.1. Objectives                                      | 24 |

| 4.2. Parts List                                      | 24 |

| 4.3. Background.                                     | 24 |

| 4.4. Tasks                                           | 31 |

| 4.5. Resources.                                      | 31 |

| 4.6. Grading Sheet                                   | 31 |

| 5. Experiment 5: Analog Input and Output             | 31 |

| 5.1. Objectives                                      | 32 |

| 5.2. Parts List                                      | 32 |

| 5.3. Background                                      | 32 |

| 5.4. Tasks                                           | 36 |

| 5.5. Resources                                       | 36 |

| 5.6. Grading Sheet                                   | 36 |

| 6. Experiment 6: Pulse-Width Modulation              | 36 |

| 6.1. Objectives                                      | 36 |

| 6.2. Parts List                                      | 36 |

| 6.3. Background.                                     | 37 |

| 6.4. Tasks                                           | 41 |

| 6.5. Resources                                       | 41 |

| 6.6. Grading Sheet                                   | 41 |

| 7. Experiment 7: Serial Communication                | 41 |

|    | 7.1. Objectives                                               | . 42 |

|----|---------------------------------------------------------------|------|

|    | 7.2. Parts List                                               | . 42 |

|    | 7.3. Background                                               | . 42 |

|    | 7.4. Tasks                                                    | . 48 |

|    | 7.5. Resources                                                | . 48 |

|    | 7.6. Grading Sheet                                            | . 49 |

| 8. | Experiment 8: Microcontroller on an FPGA                      | . 49 |

|    | 8.1. Objectives                                               |      |

|    | 8.2. Parts List                                               | . 49 |

|    | 8.3. Background                                               | . 50 |

|    | 8.4. Tasks                                                    | . 57 |

|    | 8.5. Resources                                                | . 58 |

|    | 8.6. Grading Sheet                                            | . 58 |

| 9. | Programming Assignment: Seven-Segment Display and C Libraries | . 58 |

|    | 9.1. Objectives                                               | . 59 |

|    | 9.2. Parts List                                               | . 59 |

|    | 9.3. Background                                               | . 59 |

|    | 9.4. Tasks                                                    | . 61 |

# 1. Experiment 1: Development Platform

Ahmad Khayyat; Hazem Selmi; Saleh AlSaleh 162, 13 February 2017

# 1.1. Objectives

• Get familiar with the development platform:

Hardware

microcontroller, development board, peripherals

Software

IDE, compiler, debugging, programming

- General-purpose input/output (GPIO): digital output

- Introduce CMSIS: Cortex Microcontroller Software Interface Standard

# 1.2. Parts List

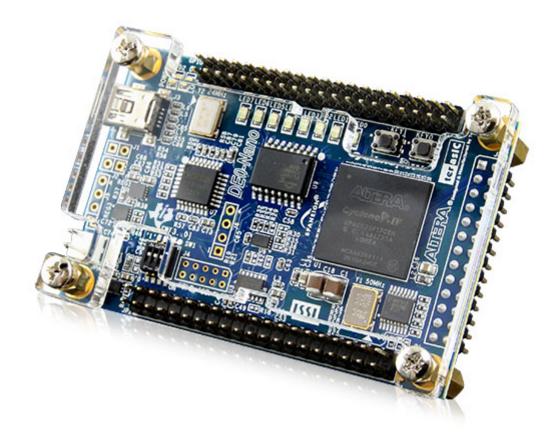

• LPC1769 LPCXpresso board

• USB A-Type to Mini-B cable

# 1.3. Background

### 1.3.1. Microcontroller

LPC1769 is a microcontroller manufactured by NXP. LPC1769 is only one member of a big family of microcontolles. NXP was founded by Philips as Philips Semiconductors, and renamed NXP in 2006. A major difference between a microcontroller and a microprocessor is that the former has some additional built-in

devices, such as memory, I/O peripherals, and timers.

The LPC1769 microcontroller is an ARM 32-bit Cortex-M3 microcontroller. Some of its features include: CPU clock up to 120MHz, 512kB on-chip Flash ROM, 64kB RAM, Ethernet 10/100 MAC, USB 2.0 full-speed Device controller and Host controller, four UARTs, general purpose I/O pins, 12-bit ADC, 10-bit DAC, four 32-bit timers, Real Time Clock, System Tick Timer.

The product data sheet for the LPC1769 microcontroller [lpc1769-data-sheet] and the more detailed user munual [lpc1769-manual] are essential resources for any developer.

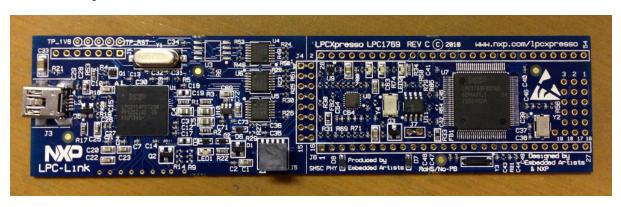

### 1.3.2. Development Board

The LPC1769 microcontroller chip is used to build the *LPC1769 LPCXpresso board*, which we will be using in this LAB.

The LPCXpresso board consists of two parts:

- 1. LPCXpresso target board, which hosts the LPC1769 microcontroller

- 2. LPC-Link: a debug probe for debugging and the target microcontroller.

### 1.3.3. LPCXpresso IDE

The LPCXpresso IDE is an Eclipse-based software development environment for NXP's LPC microcontrollers.

The LPCXpresso IDE uses the GNU toolchain (compiler and linker), and offers the choice of two C libraries:

- Redlib (default): a proprietary ISO C90 standard C library, with some C99 extensions. Often results in smaller binary size.

- Newlib: an open source complete C99 and C++ library.

The LPCXpresso IDE is available in two editions:

- Free edition: requires free activation (details below). Supports code sizes up to 256 kB after activation.

- Pro edition: per-seat licensing fees. Supports unlimited code size.

#### Installation

To install your copy of the LPCXpresso IDE:

- 1. Using a web browser, navigate to the LPC Microcontroller Utilities page, then follow the LPCXpresso IDE link.

- 2. Use the *Download* button to go to the download page, then use the download link that matches your operating system.

You may need to create an account to access the download page.

3. Run the downloaded installer.

#### **Activation**

To activate your copy of the LPCXpresso IDE:

Using a web browser, log into the activation web page: https://lpcxpresso-activation.nxp.com/registerapp.html

Register a new account if you do not have one.

2. Follow the instructions on that page to find and submit your LPCXpresso IDE serial number, and to obtain and use your activation code.

For more information on installing and using the LPCXpresso IDE, see [lpcxpresso-ide-user-guide].

### 1.3.4. Input/Output Ports

The LPC1769 microcontroller has five input/output (I/O) ports. Each port is 32 bits. However, not all of them are available for the developer. For example, pins 12, 13, 14, and 31 of port 0 are not available, leaving only 28 pins of port 0 available for the user.

Each of the I/O pins can be referred to using the port number and the pin number. For example, P0.17 or P0[17] is pin 17 in port 0, and P1.22 or P1[22] is pin 22 in port 1.

Most of the I/O pins have multiple functions. For example: P0.10 can perform one of these jobs:

P0[10]

General purpose digital input/output pin.

TXD2

Transmitter output for UART2.

SDA2

I2C2 data input/output.

MAT3[0]

Match output for Timer 3, channel 0.

Don't worry if you don't understand these functions, you will learn about them throughout the course.

A command is needed to choose which function is to be used in a specific pin. The only exception is the first function (GPIO) because it is the default function.

Relying on a default value may be acceptable in simple programs. However, a good programming style when you have many functions and interrupts is not to assume any default value as they may have been changed somewhere in your program. Instead, you should explicitly specify any desired values.

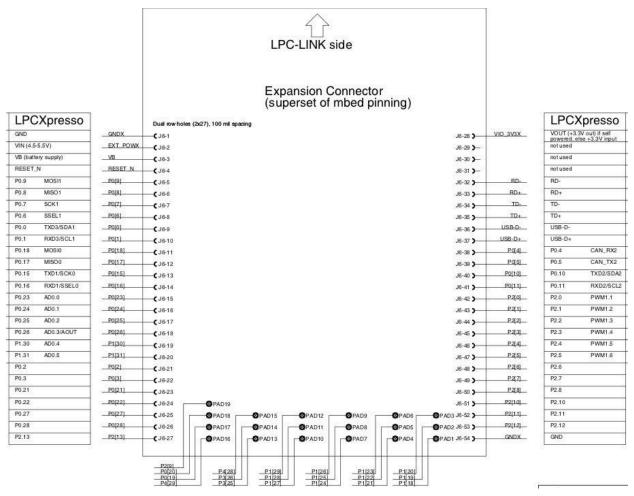

### Pin Layout

The pin layout of the LPC1769 LPCXpresso board is shown in the LPC1769 pin layout figure below (source: [lpc1769-schematic], page 7).

Figure 1. LPC1769 pin layout

#### Memory-Mapped I/O

ARM uses memory-mapped I/O. When using memory-mapped I/O, the same address space is shared by memory and I/O devices. Some addresses represent memory locations, while others represent registers in I/O devices. No separate I/O instructions are needed in a CPU that uses memory-mapped I/O. Instead, we can use any instruction that can reference memory to move values to or from memory-mapped device registers.

#### General-Purpose Input/Output (GPIO)

GPIO is available in most I/O pins. A GPIO pin is a pin that can be used for digital input or digital output. You need to choose the direction of the pin (whether it is used for input or output). In the first example of this experiment, we will set the direction to be output. To use a digital output pin, you need to be able to to *set* the output to HIGH (1), and to *clear* it to LOW (0).

In summery, we need to learn about 3 registers for our first experiment:

- 1. The register that controls the direction of GPIO pins

- 2. How to set a pin to HIGH.

- 3. How to *clear* a pin to LOW.

#### **Accessing Registers**

Each I/O register has an address. For example:

- 1. The address of the register that controls the direction of port 0 pins is: 0x2009c000.

- 2. The address of the register that sets port 0 pins to HIGH is: 0x2009c018.

3. The address of the register that *clears* port 0 pins to LOW is: 0x2009c01c.

#define CLR\_P0 (\*((volatile unsigned long \*) 0x2009c01c))

To access a register more easily, you can give it a name. One way to give a register a name in the C programming language is to use *pointers*, *pointer dereferencing*, and the define directive.

For more details about these features (and more) of the *C programming language*, it is strongly recommended to consult the document Data Structures in C.

#### Example 1. Giving Registers Names

Here are three examples showing how to assign names to registers:

#define DIR\_P0 (\*((volatile unsigned long \*) 0x2009c000))

#define SET\_P0 (\*((volatile unsigned long \*) 0x2009c018))

```

Example 2. Setting Pin Direction

```

To set the direction for pins 1, 2, 3 and 4 of port 0 as output, while setting the direction of the remaining pins as input:

```

DIR_P0 = 0x0000001E;

// OR

DIR_P0 = 30;

// Make sure that you understand that these statements are equivalent!

```

The first task is to blink an LED using the above three registers!

In the first experiment, you can avoid making any external connections by using the on board LED, which is connected to P0.22.

### 1.3.5. CMSIS

The *Cortex Microcontroller Software Interface Standard* (CMSIS) is a vendor-independent hardware abstraction layer for the Cortex-M processor series [...]. The CMSIS enables consistent device support and simple software interfaces to the processor and the peripherals, simplifying software re-use [...].

```

— ARM Ltd., CMSIS: Introduction

```

The CMSIS components are: CMSIS-CORE, CMSIS-Driver, CMSIS-DSP, CMSIS-RTOS API, CMSIS-Pack, CMSIS-SVD, CMSIS-DAP, CMSIS-DAP [cmsis-intro].

The most relevant component to us is CMSIS-CORE [cmsis-core].

CMSIS-CORE implements the basic run-time system for a Cortex-M device and gives the user access to the processor core and the device peripherals. In detail it defines:

- Hardware Abstraction Layer (HAL) for Cortex-M processor registers with standardized definitions for the SysTick, NVIC, System Control Block registers, MPU registers, FPU registers, and core access functions.

- **System exception names** to interface to system exceptions without having compatibility issues.

- **Methods to organize header files** that makes it easy to learn new Cortex-M microcontroller products and improve software portability. This includes naming conventions for device-specific interrupts.

- Methods for system initialization to be used by each MCU vendor. For example, the standardized SystemInit() function is essential for configuring the clock system of the device.

- **Intrinsic functions** used to generate CPU instructions that are not supported by standard C functions.

- A variable to determine the **system clock frequency** which simplifies the setup the SysTick timer.

— ARM Ltd., CMSIS-CORE: Overview

CMSIS provides abstraction at the chip level only. Other libraries provide more extensive APIs for additional peripherals and board features, but are usually less generic and more vendor-specific [lpcx-cmsis].

### 1.3.6. Accessing Registers Using CMSIS

When using CMSIS, you don't need to know register addresses, which implies that you don't need to use the #define directive to name the registers. Instead, you use the #include directive to include the lpc17xx.h header file, which contains all the register address definitions for the LPC17xx family of microcontrollers. When you use the LPCXpresso IDE to create a CMSIS project, the IDE generates a basic source file which already includes this header file.

In the lpc17xx.h header file, the names are not given using the #define directive only. They are given using #define (for the base address) then using structures to group similar (and adjecent) registers.

#### **Structures and Pointers**

The CMSIS header file, lpc17xx.h, organizes the registers into logical groups based on their functions, using C structures. First, a structure is defined by listing its fields. Then, a pointer is defined for each needed instance of that structure, pointing to the starting address of the instance, as documented in the microcontroller manual.

For example, the names of the pointers to the structure instances for the five GPIO ports are:

LPC\_GPI00

for port 0

LPC\_GPI01

for port 1

```

for port 2

LPC_GPI03

for port 3

LPC_GPI04

for port 4

```

These pointers are defined in the <a href="lpc17xx.h">lpc17xx.h</a> file as follows:

```

#define LPC_GPI00 ((LPC_GPI0_TypeDef *) LPC_GPI00_BASE)

#define LPC_GPI01 ((LPC_GPI0_TypeDef *) LPC_GPI01_BASE)

#define LPC_GPI02 ((LPC_GPI0_TypeDef *) LPC_GPI02_BASE)

#define LPC_GPI03 ((LPC_GPI0_TypeDef *) LPC_GPI03_BASE)

#define LPC_GPI04 ((LPC_GPI0_TypeDef *) LPC_GPI04_BASE)

```

where LPC\_GPIO\_TypeDef is the name of the structure, which is defined earlier in the file to describe the registers related to GPIO ports, and LPC\_GPIO0\_BASE through LPC\_GPIO4\_BASE are fixed addresses, also defined earlier in the header file, at which the registers for each port start. Other structures are also defined for registers related to functions other than GPIO.

#### Fields are Registers

For each instance of a structure, such as LPC\_6PIOO, you can access a register by accessing the corresponding field in that structure instance. For example, the three registers used in Experiment 1 are defined in the aforementioned LPC\_6PIO\_TypeDef structure as the following fields:

- 1 FIODIR

- 2. FIOSET

- 3. FIOCLR

Each of these registers is accessible within the structure instance of each port.

Therefore, when using CMSIS, you need to know two names to access a register:

- 1. The name of the pointer to the structure instance.

- 2. The name of the field within the structure, corresponding to the desired register.

Example 3. Setting Pin Directions and Values

• To set the direction of pins 3,4, 5, and 6 in port 2 as output (and set the remaining pins as input):

```

LPC_GPI02->FIODIR = 0x00000078;

```

• To set pins 3 and 7 in port 1 while clearing the rest of the pins, use:

```

LPC_GPI01->FIOSET = 0x00000088;

```

Again, to learn more about structures and pointers in the *C programming language*, refer to the Data Structures in C document.

#### 1.3.7. LEDs

- · What is an LED?

- · How does an LED work?

- What is the maximum voltage that an LED can tolerate?

- If the output voltage is higher than the LED maximum voltage, what should you do?

An LED should be connected to an output GPIO pin.

#### GPIO, Revisited

The GPIO mode is available in all I/O pins. A GPIO pin is one that can be used as a digital input or digital output. Obviously, you need to choose the direction of the pin to determine whether it is going to be used as input or output. In this experiment, we will choose the direction to make the required pin work as GPO (General-Purpose Output). In this case (GPO), you need a command to set this output pin to HIGH (1), and a command to Clear it to LOW (0).

A 0 in a SET or a CLR register has no effect on the port pins!

A basic way to add *delay* is to use a for loop, e.g.: for(i=0;i<500000,i++);. You will learn about more sophisticated and accurate ways in later experiments.

# 1.4. Tasks

### 1.4.1. Create a Non-CMSIS Project

- 1. Click Quickstart Panel > New project....

- 2. Choose *LPC13* / *LPC15* / *LPC17* / *LPC18* > *LPC175x* 6x > *C Project*.

- 3. Choose a project name, e.g. blinky.

- 4. In the *Target selection* dialog, choose *LPC1700 > LPC1769*.

- 5. In the CMSIS Library Project Selection dialog, set CMSIS Core library to link project to to None.

- 6. In the CMSIS DSP Library Project Selection dialog, set CMSIS DSP Library to link project to to None.

- 7. Uncheck *Enable linker support for CRP*, then click *Finish*.

- 8. Open the main source file named after the project, and write your main function.

#### 1.4.2. Blink an LED without CMSIS

1. Figure out which pin is connected to the LED.

Refer to the LPC1769 board documentation.

- 2. Give the required registers some friendly names using the #define directive.

- 3. In an infinite loop inside the main function:

- a. Set the pin to act as output by setting the correct bit in the direction register to 1.

- b. Set the output pin to 1.

- c. Clear the output pin (set to 0).

- d. Insert a delay loop after both set and clear, to be able to see the LED blink.

- 4. Which value of the pin turns the LED on, and which value turns it off? and why?

### 1.4.3. Import the CMSIS Libraries

- 1. Click Quickstart Panel > Import project(s)

- 2. In the *Project archive (zip)* dialog, click *Browse* next to the *Archive* field, and choose:

C:\nxp\LPCXpresso\_<version>\lpcxpresso\Examples\NXP\LPC1000\LPC17xx\LPC17xx\_LatestCMSIS\_Librarie

s.zip

3. Keep both projects selected: CMSIS\_CORE\_LPC17xx and CMSIS\_DSPLIB\_CM3, and click Finish.

# 1.4.4. Create a CMSIS Project

To create a project that uses CMSIS, follow the same instructions for creating a non-CMSIS project up to the *CMSIS Library Project Selection* dialog. Instead of None, select CMSIS\_CORE\_LPC17xx.

### 1.4.5. Blink an LED Using CMSIS

Using a CMSIS project, rewrite your LED blinking program to use CMSIS facilities.

### 1.4.6. Debug Your Project

- 1. Click *Quickstart Panel > Build 'cmsis\_blinky' [Debug]* to build the project.

- 2. Connect the LPC1769 board to the PC using the USB cable.

- 3. Click *Quickstart Panel > Debug 'cmsis\_blinky'* [*Debug*] to debug the project interactively on the target board.

Running the Debugger

You can run the debugger using any of the following three ways:

- 1. In the *Quickstart Panel* at the lower left corner, click *Debug '<project-name>'* [Debug].

- 2. In the main menu, choose  $Run > Debug \ As > C/C++ \ (NXP \ Semiconductors) \ MCU$  Application.

- 3. In the toolbar, click on the debug button 🕸 🕶

- 4. Once the debugger starts, it will pause execution at the first statement in the progrm. Resume execution by hitting the F8 key, or using the resume button in the toolbar.

# 1.5. Resources

$\prod$

[]

NXP Semiconductors. LPC1769/68/67/66/65/64/63 — Product data sheet. Rev. 9.5. 24 June 2014.

http://www.nxp.com/documents/data\_sheet/LPC1769\_68\_67\_66\_65\_64\_63.pdf

[]

NXP Semiconductors. UM10360 — LPC176x/5x User Manual. Rev. 4.1. 19 December 2016. http://www.nxp.com/documents/user manual/UM10360.pdf

NXP Semiconductors. *LPCXpresso IDE User Guide*. Rev. 8.1. 31 May 2016. http://www.nxp.com/assets/documents/data/en/user-guides/LPCXpresso\_IDE\_User\_Guide.pdf []

Embedded Artists AB. Board Schematics for current LPC1769 board—LPCXpresso LPC1769 rev B. 11 February 2011.

http://www.embeddedartists.com/sites/default/files/docs/schematics/LPCXpressoLPC1769revB.pdf

II

Data Structures in C.

http://www.ccse.kfupm.edu.sa/~akhayyat/files/coe306-162/lab-manual/data-structures-in-c.html

# 1.6. Grading Sheet

| Task                       | Points |

|----------------------------|--------|

| Blink an LED without CMSIS | 4      |

| Blink an LED using CMSIS   | 4      |

| Debug your project         | 2      |

# 2. Experiment 2: General-Purpose Input/Output (GPIO)

Ahmad Khayyat; Hazem Selmi; Saleh AlSaleh 162, 17 February 2017

# 2.1. Objectives

- Using GPIO pins as input and output

- Interfacing with external LEDs, switches, and push-buttons

- Bit manipulation in C

# 2.2. Parts List

- LPC1769 LPCXpresso board

- USB A-Type to Mini-B cable

- Breadboard

- LEDs

- 330-Ohm Resistors

- Jumper wires

# 2.3. Background

# 2.3.1. Bit Manipulation in C

The core of embedded system programming is setting (or clearing) specific bits in different registers inside the microcontroller. This highlights the importance of *bit manipulation* as a programming skill.

Most modern architectures are byte-addressable: the smallest unit of data is the byte. Nonetheless, it is possible to operate on individual bits by clever use of bitwise operators.

#### **Bitwise Operators**

Bitwise operators apply to each bit of their operands.

| Operator | Function    | Examples                        |

|----------|-------------|---------------------------------|

| 8        | Bitwise AND | 0011 8 0101 = 0001<br>3 8 5 = 1 |

| 1        | Bitwise OR  | 0011   0101 = 0111              |

| ٨        | Bitwise XOR | 0011 ^ 0101 = 0110<br>3 ^ 5 = 6 |

| ~        | Bitwise NOT | ~00110101 = 11001010            |

| <<       | Shift left  | 3 << 2 = 12                     |

| >>       | Shift right | 8 >> 2 = 2                      |

In C, numbers can be written in decimal, octal, or hexadecimal, but not in binary, e.g. 16 = 020 = 0x10.

Right-shifting in C is implementation-specific. Often, *logical shifting* is applied to unsigned values, whereas *arithmetic shifting* is applied to signed values.

#### **Masking**

A simple assignment to a 32-bit register or memory location will overwrite all 32 bits. However, manipulating specific bits implies that the remaining bits in the register remain intact. An essential technique to achieve that is bit masking.

A mask is a value that can be used in a binary, i.e. two-operand, bitwise operation to change specific bits of some other value. Masking relies on the following rules of Boolean Algebra:

- ANDing a bit with a 0 results in a 0. ANDing a bit with a 1 results in the same bit.

- ORing a bit with a 0 results in the same bit. ORing a bit with a 1 results in a 1.

- XORing a bit with a 0 results in the same value. XORing a bit with a 1 inverts the bit.

#### **Exercises**

- 1. What mask and bitwise operation are required to set the third least significant bit (bit 2) to 1 without affecting the other bits in a 32-bit variable x?

- 2. What mask and bitwise operation are required to reset bit 10 of a 16-bit variable y to 0?

- 3. What mask and bitwise operation are required to toggle bit 20 of a 32-bit variable z?

#### **Creating Masks by Shifting**

If you have worked out the exercises above, you would have noticed that spelling out masks can be tedious, verbose, and error-prone. One trick that makes it easier to create masks is to use the shift operations. For example, to create a mask whose bit 10 is 1 and whose other bits are 0, you can use the following C statement:

```

mask = 1 << 10;

```

#### **Exercise**

Repeat the three exercises above by using shift operations to create the masks.

### 2.3.2. Digital Input

A GPIO pins can be configured to act as a general-purpose input pin by setting the corresponding bit in the FIODIR register to 0. A digital input pin is *digital* because it is *driven* by an external digital device that has only two states (HIGH or LOW); and it is *input* because its state is *read* by the microcontroller. That implies that some external device/circuit is needed to generate that digital input value (HIGH or LOW).

Examples for simple digital input devices include switches and push-buttons.

A common mistake is to forget about or misuse the FIODIR register.

#### The FIOPIN Register

In addition to the three registers used in Experiment 1 (FIODIR, FIOSET, and FIOCLR), there are a few additional GPIO-related registers. The one that is particularly essential for reading from a digital input peripheral is FIOPIN.

This register is a R/W register that stores the current state of a port's pins. In other words, you can write to FIOPIN to set and clear pins of a specific port. You can also read the state of port pins. FIOPEN is essential for the read operation, but since it is a R/W register, it can also be used with output pins. For instance, you can redo Experiment 1 using FIOPIN only instead of FIOSET and FIOCLR.

There is an FIOPIN register for each one of the five I/O ports, and it can be accessed in the same way FIOSET and FIOCLR are. For example, port 1's FIOPIN register can be accessed using:

```

LPC_GPIO1->FIOPIN

```

Example 4. Using the FIOPIN Register

```

To set the third bit of port 0, i.e. P0[2]:

LPC_GPIO0->FIODIR |= (1 << 2); // configure the pin for output

LPC_GPIO0->FIOPIN |= (1 << 2); // set the the pin value to high or one

LPC_GPIO0->FIOPIN &= ~(1 << 2); // clear the pin value, set its value to be low or zero

```

#### 2.3.3. Debugging

The LPCXpresso IDE along with LPC-Link hardware provide the ability to step through the code by executing one statement or instruction at a time. This helps find which line in the code causes some errors or invalid values.

To step through the program statements or instructions, run it by pressing F6 instead of F8. This will execute the code one statement at a time.

You can add a breakpoint to a statement and the debugger will stop at that statement only.

You can learn more about LPCXpresso's debugging support by referring to the [lpcxpressoide-user-guide].

In particular, you may want to check out section 3.4.2 Controlling Execution, which lists all the possible ways to step through your code, such as stepping into and stepping over functions.

#### **Inspect Variable Values at Runtime**

After uploading a program to the microcontroller, start debugging it by stepping through the statements or by adding a breakpoint. Now, you can get the value of any variable simply by hovering the mouse over the variable in the code. A window will be shown containing details about the variables such as type and value.

This can also be used for registers. For example, you can use it to find the value of  $LPC\_GPIOO \rightarrow FIOPIN$ .

#### **Print Variable Values**

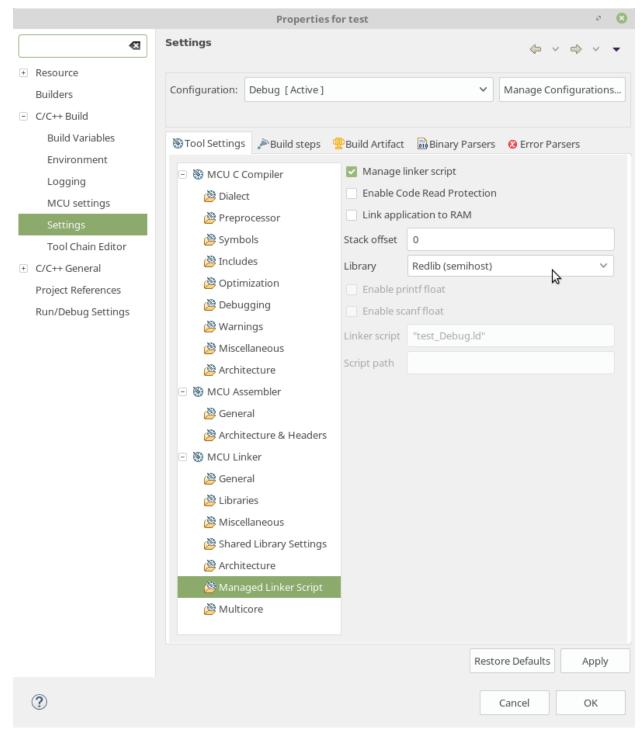

To be able to use the printf function to print variables to the console:

- 1. Right Click on the project's name and then click on *Properties*.

- 2. Expand *C/C++ Build* and select *Settings*.

- 3. Under MCU Linker, click on Managed Linker Script.

- 4. Change the *Library* used from *Redlib* (none) to *Redlib* (semihost), as shown in the Semihost Debugging Configuration figure.

This is a limited implementation of the printf function that does not recognize all format specifiers, but is sufficient for most debugging needs.

#### Example 5. Using the printf Function

```

printf("push-button value: %d\n", value);

// Given that value is an integer (int) containing the state of a push button

```

Figure 2. Semihost Debugging Configuration

# 2.4. Tasks

In this experiments, you will control LED lights by software.

#### 2.4.1. Hardware

- 1. Find out which I/O Pins you *can* use for controlling LEDs, and choose specific ones.

- 2. Connect four LEDs using a proper current-limiting resistor.

- 3. Connect two switches using a proper current-limiting resistor.

#### 2.4.2. Software

#### Blink an LED using FIOSET and FIOCLR

Pick an LED and blink it using only one FIOPIN statement and one delay loop!

Use bitwise exclusive-OR.

#### **Implement LED Scrolling**

- 1. Write a program that makes it look like the light is scrolling through 4 LEDs that are connected externally. The scroll effect can be achieved by turning LEDs ON and OFF sequentially.

- 2. Use two switches to control the scrolling. For example, you can use one switch to turn the scrolling ON and OFF, and the second switch to reverse the scroll direction.

# 2.5. Resources

П

NXP Semiconductors. *LPCXpresso IDE User Guide*. Rev. 8.1. 31 May 2016. http://www.nxp.com/assets/documents/data/en/user-guides/LPCXpresso\_IDE\_User\_Guide.pdf

# 2.6. Grading Sheet

| Task                         | Points |

|------------------------------|--------|

| Using FIOPIN with XOR        | 4      |

| Using FIOPIN with input pins | 4      |

| Discussion                   | 2      |

# 3. Experiment 3: Interrupts

Hazem Selmi; Ahmad Khayyat 162, 24 February 2017

# 3.1. Objectives

- Understand interrupts in LPC1769

- Introduce the PINSELx registers

- Using external interrupts

# 3.2. Parts List

- LPC1769 LPCXpresso board

- USB A-Type to Mini-B cable

- Breadboard

- LEDs

- Push-buttons or switches

- 330-Ohm Resistors

- · Jumper wires

# 3.3. Background

Interrupts are essential for embedded systems. The information in this experiment will be used in all future experiments in this lab.

### 3.3.1. Interrupts in LPC1769

Interrupts allow for suspending the currently executing code, and having the CPU switch to execute a routine associated with the received interrupt request.

In LPC1769, there are 35 hardware interrupts. Each interrupt is identified by a number called IRQn, or *Interrupt ID* as called in the LPC1769 manual. Below are some examples of hardware interrupts and their IDs:

Table 1. Example Interrupt IDs

| Interrupt ID | Interrupt Source       |

|--------------|------------------------|

| 1            | Timer 0                |

| 2            | Timer 1                |

| 5            | UART 0                 |

| 6            | UART 1                 |

| 13           | SPI                    |

| 18           | EINT0                  |

| 19           | EINT1                  |

| 20           | EINT2                  |

| 21           | EINT3                  |

| 33           | USB Activity Interrupt |

In CMSIS, interrupts are numbered from 0 to 34.

In addition to these 35 interrupts, there are 8 exceptions with negative numbers. Exceptions are not discussed in this experiment.

#### Exercise

Find the interrupt number definitions of the LPC1769 in the lpc17xx.h header file.

#### **Setting up Interrupts in LPC1769**

There are four main steps to correctly setup any interrupt in LPC1769:

- 1. Configure the required peripheral to generate interrupt requests. For example, to be able to use a timer interrupt, a timer must be activated and configured to generate interrupt requests.

- 2. Enable the interrupt in the *Nested Vectored Interrupt Controller (NVIC)*. See Enabling the Interrupt in the NVIC for more information about the NVIC.

- 3. Write an *interrupt service routine (ISR)*: the routine that needs to be executed when an interrupt request is received.

4. Clear the interrupt request at the end of the ISR to allow future requests of the same interrupt.

Some peripherals that are capable of generating interrupts can also be used without interrupts. There are valid uses for either approach. That's why it is required to configure devices to generate interrupt requests when that behavior is desired (step 1 in the list above).

Upon setting up an interrupt as described above, the LPC1769 microcontroller will be responsible for:

- Detecting the interrupt request generated by a peripheral. This request will be generated by the peripheral that has been enabled by software.

- Jumping to the interrupt service routine associated with that request.

#### 3.3.2. Configuring Microcontroller Interrupts

This section elaborates the four steps listed in the previous section (Setting up Interrupts in LPC1769) to configure the LPC1769 microcontroller to handle interrupt requests generated by a given device.

The programmer must perform four main steps:

- 1. Enable a peripheral to generate a hardware interrupt request (not to be discussed here because it is peripheral dependent)

- 2. Enable the required interrupt in the NVIC

- 3. Write an interrupt service routine (ISR)

- 4. Clear the interrupt request at the end of the ISR

#### **Enabling the Interrupt in the NVIC**

The Nested Vectored Interrupt Controller (NVIC) offers very fast interrupt handling and provides the vector table [keil-nvic].

In addition, the NVIC:

- Saves and restores automatically a set of the CPU registers (R0-R3, R12, PC, PSR, and LR).

- Does a quick entry to the next pending interrupt without a complete pop/push sequence.

- Provides many other advanced features.

#### **NVIC** Functions

The CMSIS core module defines a set of interrupt helper functions. For example, to enable interrupts for a given interrupt ID, you can use the function:

```

NVIC_EnableIRQ(IRQn); // IRQn is the interrupt ID

```

For example, for UART1, IRQn is 6 (see Example Interrupt IDs Table). You can use this number or use the given name in lpc17xx.h: UART1\_IRQn.

#### The ISR

Whenever an interrupt request is generated, the CPU will jump to the corresponding ISR. When using CMSIS, the ISR is a C function that has the following prototype format:

```

void __peripheral___IRQHandler();

```

#### Example 6. An ISR for the TIMER2 Device

```

void TIMER2_IRQHandler() {

// Your code goes here

// Clear the interrupt request at the end of the ISR

}

```

#### **Clearing the Interrupt Request**

As indicated in the format of the ISR above, the last statement in any ISR should be to clear the request that has just been served. This is required to allow future requests of the same interrupt.

This step is peripheral-dependent and is usually done by clearing a bit in one of the peripheral registers.

#### **Other Interrupt-Related Operations**

Interrupts will not function at all without the above four steps. There are other issues, however, that are not essential in simple applications, but can be very useful and even essential in some applications, especially when you have multiple interrupts. We will discuss two such issues here:

- 1. Interrupt status

- 2. Interrupt priority

#### **Interrupt Status**

Sometimes, you need to check the status of a specific interrupt. For example, is it pending, active or disabled.

When using CMSIS, the status of interrupts can be checked by calling one of the following functions, depending on the application:

- uint32\_t NVIC\_GetPendingIRQ(IRQn\_Type IRQn)

- If the interrupt status is *not pending*, the function returns **0**.

- If the interrupt status is *pending*, the function returns 1.

- uint32\_t NVIC\_GetActive(IRQn\_Type IRQn)

- $\circ~$  If the interrupt status is *not active*, the function returns 0.

- If the interrupt status is *active*, the function returns 1.

#### **Interrupt Priority**

When using CMSIS, you can set interrupt priorities by calling the function:

```

void NVIC_SetPriority(IRQn_Type IRQn, uint32_t priority)

```

- The fist argument is the interrupt ID.

- The second argument represents the priority, where 0 is the highest priority and 31 is the lowest priority.

To assign a different priority for each interrupt, you need to call this function for every interrupt you are using.

#### 3.3.3. External Interrupts

To practice interrupts, we will concentrate on external interrupts only in this experiment, since other hardware interrupts require understanding the functions with which they are associated, which we did not cover yet.

One type of interrupts that is easy to experiment with is external interrupts. They are the interrupts that are generated by a device outside the microcontroller. An external interrupt should be connected to one of the I/O port pins.

In external interrupts, an interrupt request is generated by a pulse at a pin that has been enabled to accept external interrupt requests. A simple way to implement that is to use a push-button to generate that request.

The difference between such implementation and what you did in Experiment 2 is that in Experiment 2, we used *polling*, where the CPU is always busy reading the pin in order to detect a change that would trigger some action. When using interrupts, however, the CPU is available to execute other code. When the pushbutton is pressed, the CPU stops whatever it is doing and jumps to the routine associated with that interrupt request.

There are four external interrupt channels available to the developer, called EINT0, EINT1, EINT2 and EINT3. In older ARM versions, a pin's function must be set for the pin to act as an external interrupt. This is done using the PINSELx register (see The PINSELx Registers). However, one of the new features of the newer Cortex family is accepting external interrupts from some GPIO pins! Any GPIO pin used for external interrupts will be using external interrupt channel 3 (EINT3).

You can use GPIO pins from ports 0 and 2 only for external interrupts. You have about 40 different pins to choose from. Compare that, for example, to ARM7 where only 7 pins are available for external interrupts.

External interrupts can be enabled on two sets of pins:

- 1. Four dedicated pins (P2.10, P2.11, P2.12 and P2.13) that act as EINT0, EINT1, EINT2, and EINT3, respectively.

- 2. Any GPIO pin in port 0 and port 2.

In the two following sections, we will discuss and practice:

- GPIO external interrupts

- Non-GPIO external interrupts

#### **GPIO** external interrupts

As discussed in Setting up Interrupts in LPC1769, you always need to enable the NVIC and write an ISR.

For GPIO external interrupts, that leaves two more steps:

- 1. Activating GPIO external interrupts

- 2. clearing a GPIO interrupt request at the end of the ISR

#### **Activating GPIO External Interrupts**

To activate external interrupts on a GPIO pin, you only need to configure whether the pin is to generate an interrupt request on the rising edge or on the falling edge.

You can set external interrupts to be generated on the *rising edge* on a GPIO pin by setting the IO0IntEnR and IO2IntEnR registers, depending on the port to which the pin belongs. These names refer to 32-bit registers. Setting a bit to 1 enables rising-edge interrupts at the corresponding pin.

To generate interrupts on the *falling edge*, you can use the <code>IOOIntEnF</code> and <code>IO2IntEnF</code> registers instead.

In LPC17xx.h, the structure that deals with GPIO external interrupts is LPC\_GPIOINT, which includes a few fields that control the GPIO pins when acting as an external interrupt.

Example 7. Enable Rising-Edge Interrupts on Pin 0 of Port 2 Only

```

LPC_GPIOINT->IO2IntEnR = 1;

```

#### **Clearing External GPIO Interrupt Requests**

To clear the interrupts of a port pin, set the corresponding bit to 1 in register IO0IntClr or IO2IntClr, depending on the port. Both registers are fields of the LPC\_GPIOINT structure.

#### Other issues related to GPIO interrupts

Level and Edge Sensitivity (For Non-GPIO Interrupts)

You may have noted that, to enable GPIO interrupts, you have to select whether they are triggered by the rising or falling edge of the pulse at the pin.

Interrupt Status for GPIO External Interrupts

You can check for pending GPIO interrupts by reading the appropriate status register. There are four status registers for ports 0 and 2 that indicate whether an interrupt is pending, and whether it is triggered by a rising edge or a falling edge. They are IO0IntStatR, IO2IntStatR, IO0IntStatF, and IO2IntStatF.

For Example, if bit 9 of IO2IntStatR is 1, then P2.09 has a pending rising-edge interrupt request.

This is particularly important when you have multiple interrupts sharing the same interrupt channel (EINT3 in our case). Any one of them can result in executing the same ISR. Now, If you want to perform different actions for each interrupt, you need to identify the source interrupt in order to perform the corresponding action. You can do that by checking the status registers in your ISR.

#### **Non-GPIO** external interrupts

As is the case with GPIO external interrupts, the two basic steps for using non-GPIO external interrupts are:

- 1. Activating Non-GPIO external interrupts

- 2. Clearing a Non-GPIO interrupt request at the end of the ISR

Read Setting up Interrupts in LPC1769 again!

#### **Activating Non-GPIO External Interrupts**

External interrupt requests can be generated using any of the 4 dedicated external interrupt pins, named EINT1, EINT3, and EINT4:

EINT0

P2.10

EINT1

P2.11

EINT2

P2.12

EINT3

#### Review

If an external interrupt is requested through one of the above pins, the CPU will jump to the corresponding ISR, which is a C function identified by its name as follows:

| Name  | Pin   | Handler (ISR)                      |

|-------|-------|------------------------------------|

| EINT0 | P2.10 | <pre>void EINT0_IRQHandler()</pre> |

| EINT1 | P2.11 | <pre>void EINT1_IRQHandler()</pre> |

| EINT2 | P2.12 | <pre>void EINT2_IRQHandler()</pre> |

| EINT3 | P2.13 | <pre>void EINT3_IRQHandler()</pre> |

To configure one of the above pins to act as EINTx, you must set the appropriate PINSELx register bits (see The PINSELx Registers).

#### **Exercise**

Which PINSELx register(s) and bits do you need to set to have access to each of EINTO, EINT1, EINT2, and EINT3?

Refer to the LPC1769 User Manual.

Setting the function of a pin to external interrupt (EINTx) *enables* the corresponding interrupt.

From the above, you can see that external interrupt no. 3, EINT3, can be activated in two ways:

- 1. Using PINSEL4 to activate EINT3 at P2.13; or

- 2. Using a GPIO pin from port 0 or port 2.

In other words, the EINT3 channel is shared with GPIO interrupts.

#### **Clearing External Non-GPIO Interrupt Requests**

When a Non-GPIO external interrupt request is received, an interrupt flag is set in the EXTINT register, which would assert the request to the NVIC. The four least significant bits in the EXTINT register indicate the pending external interrupts. For example, when EINTO is enabled and requested, bit 0 in EXTINT will be set to 1 by the CPU.

Active bits in the EXTINT register *must be cleared in the ISR*. Otherwise, future similar interrupt requests will not be recognized. To clear a bit in the EXTINT register, set it to 1.

The EXTINT register is also a field in the LPC\_SC structure.

For example, to clear all external interrupts:

```

LPC_SC->EXTINT |= 0xF;

```

#### Other issues related to Non-PIO interrupts

Level and Edge Sensitivity (For Non-GPIO Interrupts)

The default for non-GPIO interrupts is that LOW triggers an interrupt request. However you can change that using the EXTPOLAR and EXTMODE registers, which control the non-GPIO external interrupt behavior.

Although these registers are 32-bit, only the least significant 4 bits are used. Bit 0 controls EINT0, bit 1 controls EINT1, bit 2 controls EINT2, and bit 3 controls EINT3.

EXTMODE selects whether external interrupts are *level*-sensitive (0) or *edge*-sensitive (1).

EXTPOLAR, the External Interrupt Polarity Register, controls which level or edge on each pin will cause an interrupt (depending on EXTMODE):

- 1. If EXTMODE is set to level sensitivity, setting a bit in EXTPOLAR to a 0 specifies that the corresponding external interrupt is *LOW-active* (triggered by the 0 level), and setting it to a 1 makes it *HIGH-active* (triggered by the 1 level).

- 2. If EXTMODE is set to edge sensitivity, setting a bit in EXTPOLAR to a 0 specifies that the corresponding external interrupt is *falling-edge sensitive*, and setting it to a 1 makes it *rising-edge sensitive*.

Both EXTMODE and EXTPOLAR registers are fields of the LPC\_SC structure (SC for System Control).

### 3.3.4. The PINSELx Registers

This section is not specific to interrupts. It is about configuring the function of a pin in a port. One possible functions is *external interrupt*.

The Configuring Interrupts section above covered three of the four required steps to fully setup interrupts. The remaining step is to configure the hardware that is responsible for generating the interrupt request. This step is largely dependent on the hardware that is going to generate the request, but is always required.

Configuring the hardware involves a common step regardless of the hardware being configured. That common step is configuring the functions of the relevant pins.

Each pin can be configured to perform one of four functions. Therefore, the function of each pin is controlled by two bits, as follows:

00

Primary (default) function, (GPIO)

01

First alternate function

10

Second alternate function

11

Third alternate function

As such, to configure the functions of the five 32-bit ports, ten function selection registers are required. They are named PINSEL0, PINSEL1, PINSEL2, ..., PINSEL9. PINSEL0 controls the functions of the lower half of port 0 (P0.0 to P0.15), PINSEL1 controls the functions of pins P0.16 to P0.31, PINSEL2 controls the functions of pins P1.0 to P1.15, and so on.

For example, the two least significant bits in PINSELO control the function of pin P0.0 as follows:

OO

GPIO

O1

RD1: CAN1 receiver input

10

TXD3: Transmitter output for UART3

11

SDA1: I2C1 data input/output

(See Table 73 in the LPC1769 User Manual.)

All PINSELx registers are fields in the LPC PINCON structure.

So, to configure P0.0 to function as TXD3 instead of GPIO:

```

LPC_PINCON -> PINSEL0 = 0x00000002; // Assignments like this are not the best way, // unless you want to set the remaining pins to GPIO

```

- To avoid affecting other pins, You may want to use bitwise operations to set and/or clear the required bits in PINSELx.

- Using 00 for any pin sets its function to GPIO. The reset value for PINSELx registers is 0x00000000. That is why the default function for all I/O pins after a reset is GPIO.

- You may want to refer back to this section whenever you want a pin to have a function other than GPIO.

# **3.4. Tasks**

#### 3.4.1. One External Interrupt

- 1. Use a push-button to generate an external interrupt using a GPIO pin. Do something interesting in the ISR!

- 2. Use a push-button to generate an external interrupt using a non-GPIO pin, i.e. a pin explicitly configured for external interrupts. Use the same ISR from task 1.

#### 3.4.2. Two External Interrupts

3. Use two external interrupts, where each interrupt triggers a different task. For example, each interrupt could blink an LED 10 times at a different rate.

The faster rate interrupt should have a higher priority; if it is activated while the slow rate interrupt is being serviced, the slow rate interrupt handler will be paused to service the fast rate interrupt and then come back to the *pending* slow interrupt.

All tasks must be completed during the lab session.

# 3.5. Resources

$\prod$

ARM Ltd. 'Nested Vectored Interrupt Controller'. 2013. http://www.keil.com/support/man/docs/gsac\_gsac\_nvic.htm

[]

NXP Semiconductors. 'UM10360 LPC176x/5x User manual'. Rev. 3.1. 2 April 2014. http://www.nxp.com/documents/user\_manual/UM10360.pdf

# 3.6. Grading Sheet

| Task                                            | Points |

|-------------------------------------------------|--------|

| Task 1: External interrupt using a GPIO pin     | 2      |

| Task 2: External interrupt using a non-GPIO pin | 3      |

| Task 3: Two external interrupts with priorities | 3      |

| Discussion                                      | 2      |

# 4. Experiment 4: Hardware Timers

Hazem Selmi; Ahmad Khayyat; Mansour Alharthi 162, 10 March 2017

# 4.1. Objectives

- Using hardware timers

- Using the LPC1769 manual to figure out how to use a given register

- Identifying how to access a given register by referring to the LPC17xx.h file

# 4.2. Parts List

- LPC1769 LPCXpresso board

- USB A-Type to Mini-B cable

- Breadboard

- LEDs

- 330-Ohm Resistors

- Jumper wires

# 4.3. Background

There are four hardware timers in LPC1769: Timer 0, Timer 1, Timer 2, and Timer 3. They are identical and can work independently with different settings.

Throughout this document, *timer* or TIMERx refer to one of these LPC1769 timers. Every one of the timer-related registers discussed henceforth applies to all of these four timers, and cannot be used without specifying the targeted timer.

# 4.3.1. Timer Basic Operation: Timer Counter

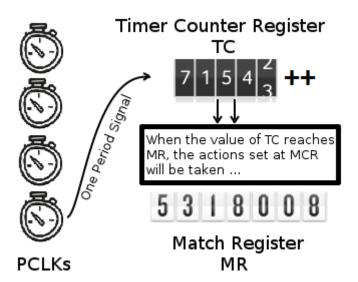

The basic function of any timer is to have a counter running. In LPC1769, this counter is called *Timer Counter* (TC).

In this section, we will learn how to enable TC to start ticking, and will find out how fast it can run.

#### **Controlling the Counting Speed**

Peripherals in LPC1769 are fed with an input clock called the peripheral clock (PCLK). By default, the *Timer Counter* (TC) register is incremented every PCLK cycle.

There are two ways to change that:

- 1. Divide PCLK by a factor other than the default. This will change the input clock frequency. Since this method is applicable for all peripherals we will discuss it in a separate section at the end of this document.

- 2. Using an intermediate counter called the *prescale counter*.

The *prescale counter* is *always* incremented every PCLK pulse. This continues till the *prescale counter* = the *prescale register*. When that happens, two events take place in the next PCLK pulse:

- Increment TC by 1

- Reset the prescale counter and continue counting

If the prescale register is not set to any value (the default is 0), TC to be incremented every PCLK.

Although it was claimed ealier that TC is by default incremented every PCLK, you now know that this is only true when the *prescale register* = 0.

Example 8. TC and the Prescale Register

If you set the  $prescale\ register$  to 5, TC will be incremented every 6 PCLK pulses.

### **Enabling the Counter**

To start using a timer, you first must enable counting! In LPC1769, the *Timer Control Register* (TCR) is the register that allows you to do that.

As should be clear from previous experiments, you interact with peripherals through registers. In the case of timers, to enable a counter and have it start counting, you need to write to the TCR register. To do that, you must:

- 1. Identify the relevant bit(s) of the register. For that, refer to table 428 in chapter 21 of the LPC1769 manual.

- 2. Find out how to access this register using CMSIS. One easy way to do that is to check the lpc17xx.h file to find the structure containing the TCR field.

#### **Exercise**

- How can you enable Timer 0 counter?

- How can you enable Timer 3 counter?

You can write a single line of code that would enable the counter, and then use printf() to see whether TC is counting.

### 4.3.2. Timer Counter (TC) is Ticking; Now What?

There are two main ways to use a ticking timer:

- 1. Load a *match register* (MR) with some value and then wait till TC=MR to trigger some action.

- 2. Capture the time in a *capture register* (CR), i.e. set CR= TC, whenever an event takes place on a given pin. The event is simply any change of the pin state (HIGH  $\rightarrow$  LOW or LOW  $\rightarrow$  HIGH, i.e. a positive edge or a negative edge).

In this section, we will discuss these two options.

#### Timing Using a Match Register

For each LPC1769 timer, there are four match registers: MR0, MR1, MR2, and MR3.

Timer Registers

Hereafter, MR or MRx refers to one of MR0, MR1, MR2, and MR3 match registers of a specific LPC1769 timer.

When the value of TC reaches the value in the *match register* (MR), an action is triggered. Therefore, setting MR specifies the timer's period. The action triggered every time TC reaches MR0 can be set using the *Match Control Register* (MCR) to one (or more) of the following:

- 1. Generate an interrupt

- 2. Reset TC

- 3. Stop TC

Figure 3. Timers in LPC1769

You can enable or disable the above actions by setting or clearing the three least significant bits of the MCR register.

Table 2. Setting Timer Actions Using the MCR Register

| MCR bit | Bit value = 1          | Bit value = 0           |

|---------|------------------------|-------------------------|

| 0       | Enable timer interrupt | Disable timer interrupt |

| 1       | Reset TC               | Disable this feature    |

| 2       | Stop TC                | Disable this feature    |

#### **External Match Action**

You can also trigger a different action when TC=MRx, which is, to *set*, *reset*, or *toggle* a specific bit. This bit can be pinned out to an external output pin, hence the name: *External Match* bit (EMx).

For each timer, there are 4 EM bits, namely EM0, EM1, EM2, and EM3. Each EMx bit can be controlled when TC equals the corresponding MRx. These four EM bits belong to the EMR register. In other words, for each MRx, the external match *control bits* and the *controllable* bit are all part of the same EMR register.

Study the EMR register tables (432 and 433) in chapter 21 of the LPC1769 manual to understand the following examples.

#### Example 9. External Match Actions

- Assigning 0 to bit 6, and 1 to bit 7 in EMR will force bit 1 in EMR to be HIGH when TC = MR1.

- Assigning 1 to both bits 10 and 11 in EMR will toggle bit 3 in EMR when TC = MR3.

Theoretically, any EM bit can be pinned out to a pin that is named MATx.y, where x is the timer number and y is the match register number.

Example 10. Pinned Out External Match Actions

- When using MR3 with Timer 2, the EM3 bit of the EMR register of Timer 2 can be pinned out to MAT2.3.

- When using MR1 with Timer 0, the EM1 bit of the EMR register of Timer 0 can be pinned out to MAT0.1.

Practically, however, only MATx.0 and MATx.1 are available in LPC1769 for Timer 0, Timer 1, and Timer 3, whereas Timer 2 can use all four MAT2.y pins.

You need to change a pin's function to use it as MATx.y. Refer to the PINSEL section in experiment 3 and chapter 8 of the LPC1769 manual for more details.

### **Exercise**

One of the tasks in this experiment is about external match actions. To be able to complete that task, you need to find a suitable MATx.y pin.

So, refer to chapter 8 of the LPC1769 manual and list all the MATx.y pins and find out which of them is physically available and accessible on your LPCXpresso board.

#### **Capturing an Event (Event Timers)**

Instead of using a *match register*, you can capture the time in a *capture register* (CR) when a pin's state changes. In other words, you can take a snapshot of the timer value when an input signal changes.

This happens by loading the TC value into a CR ( $CR \leftarrow TC$ ) when an input pin has a positive edge and/or a negative edge.

For each timer, there are two *capture registers*: CR0 and CR1. A pin that can be used with a CR is named CAPx.y, where x is the timer number and y is *capture register* number.

#### Example 11. Capture Registers

- By using CAP1.0, you will be loading TC into CR0 of Timer 1.

- By using CAPO.1, you will be loading TC into CR1 of Timer 0.

To enable this feature, you need to use the CCR register. In addition to capturing the time, you can use the CCR register to enable generating an interrupt when the state of CAPx.y changes.

Study the CCR register table (431) in chapter 21 of the LPC1769 manual to understand the following examples.

#### Example 12. Using the CCR Register

Assign 15 (1111 in binary) to the CCR register of Timer 0 will:

- Load TC to CRO on both the positive and negative edges of CAPO.O

- Generate a Timer 0 interrupt request

- Load TC to CR1 only on the positive edges of CAPO.0, without generating interrupt requests.

You need to change a pin's function to use it as CAPx.y. Refer to the PINSEL section in experiment 3 and chapter 8 of the LPC1769 manual for more details.

#### **Exercise**

One of the tasks in this experiment is about capturing event times. To be able to complete that task, you need to find a suitable CAPx.y pin.

So, refer to chapter 8 of the LPC1769 manual and list all the CAPx.y pins and find out which of them is physically available and accessible on your LPCXpresso board.

#### 4.3.3. Important Notes

- If you choose to enable the timer interrupt, remember to enable the NVIC and to clear the interrupt bit in the ISR. To clear the MRO interrupt flag, set the least significant bit in the *Interrupt Register* (IR).

- A common misconception is to assume that register MR0 can be used with timer 0 only, register MR1 with timer 1 only, and so on. Each timer has its own 4 match registers.

- As usual, all the registers in this experiment are fields of some structures. Refer to the LPC17xx.h header file to find the required name and field to access the required register.

#### **Exercise**

In this exercise, we will use a hardware timer and timer interrupts to blink an LED.

```

// "x" is a placeholder. Replace x with an appropriate value.

int main(void) {

// Try to find out the IRQ number. Why is this step important?

NVIC EnableIRQ(x);

// Answer:

// What does register TCR do?

LPC_TIMx->TCR |= x;

// Answer:

// What does register MRx do?

LPC_TIMx -> MRx = x;

// Answer:

// What does register MCR do?

LPC TIMx - > MCR = x;

// Answer:

LPC_GPIOx->FIODIR = 1 << x ;

// Can we remove this while loop? Why?

while(1);

// Answer:

return 0 ;

}

// When will the following function be executed? Who is going to call it?

// Answer:

void TIMERx_IRQHandler() {

LPC_GPIOx->FIOPIN ?? (1 << x);

// Replace "??" with the appropriate operator

// What does register IR do?

LPC_TIMx -> IR \mid = (1 << x);

}

```

# 4.3.4. Peripheral Clock (PCLK)

Timers, among other devices, rely on *peripheral clocks* (PCLK), which in turn are derived from the *core clock* (CCLK).

There are four possible frequency configurations for the peripheral clock (PCLK), which are set using a pair of bits.

Table 3. Peripheral Clock (PCLK) Frequency Configurations

| Bit Values | Frequency Configuration |

|------------|-------------------------|

| 01         | PCLK = CCLK             |

| 10         | PCLK = CCLK / 2         |

| 00         | PCLK = CCLK / 4         |

| 11         | PCLK = CCLK / 8         |

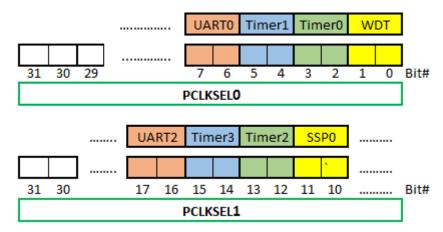

These pairs of bits belong to the PCLKSEL0 and PCLKSEL1 registers, which control the PCLK frequency for all peripherals.

The PCLKSEL0 and PCLKSEL1 Register Fields figure illustrates some of the fields of the PCLKSEL0 and PCLKSEL1 registers. Every two bits control the PCLK frequency for a specific peripheral.

Figure 4. PCLKSEL0 and PCLKSEL1 Register Fields

#### Question

Can you ignore this step? What would happen if we skip it?

- For the full list of peripherals and their corresponding two bits in PCLKSEL0 or PCLKSEL1, you can refer to Chapter 4 (section 4.7.3) in the LPC1769 manual.

- This section is not specific to timers. It is about configuring the frequency of PCLK, which is required for timers.

- You may want to refer back to this section whenever you want to use a peripheral that requires PCLK.

# 4.3.5. Power Up

All microcontroller peripherals must be powered up before they can be used. This was not a concern in earlier experiments because we were using peripherals that are powered up by default.

Powering peripherals up and down is controlled through the *Power Control for Peripherals Register* (PCONP).

By referring to table 46 in Chapter 4 of the LPC1769 manual, you can see that the reset value (default value) is 1 for some peripherals, meaning that they are powered on by default, whereas it is 0 (OFF by default) for others.

```

LPC_SC -> PCONP |= (1 << xx);

// where xx is the bit number in PCONP that controls the

// power (ON/OFF) for a specific peripheral.

```

Timer 0 and Timer 1 are powered up by default. However, if you use Timer 2 or Timer 3, your experiment will not work without powering up the timer in your program.

To save power, you can turn the power OFF for any unused peripherals that are ON by default.

# 4.4. Tasks

- 1. Complete the LED blinking exercise above. Note that a for loop is not needed to implement the delay.

- 2. Blink an LED without using timer interrupts.

- 3. Connect an output pin to two capture pins, say CAP2.0 and CAP2.1. Enable one of them to capture the time with the rising edge and the other one with falling edge.

Now, set the output pin high then clear it immediately. Calculate the difference between CR0 and CR2 and use printf() to display this difference.

Can you explain the result?

Try using FIOPIN instead of FIOSET and FIOCLR to control the output pin.

Try using direct assignment or bitwise OR for masking the remaining bits.

Can you explain the different results?

Use external match actions for task 2.

# 4.5. Resources

[]

NXP Semiconductors. 'UM10360 LPC176x/5x User manual'. Rev. 3.1. 2 April 2014. http://www.nxp.com/documents/user\_manual/UM10360.pdf

# 4.6. Grading Sheet

| Task                                       | Points |

|--------------------------------------------|--------|

| Use hardware timers with Interrupts        | 4      |

| Use External match pins MATx.y             | 4      |

| Use the CAPx.y pins with capture registers | 2      |

# 5. Experiment 5: Analog Input and Output

Hazem Selmi; Ahmad Khayyat 162, 19 March 2017

# 5.1. Objectives

- Using the Analog-to-Digital Converter (ADC) to read analog input

- Using the Digital-to-Analog Converter (DAC) to write analog output

# 5.2. Parts List

- LPC1769 LPCXpresso board

- USB A-Type to Mini-B cable

- Breadboard

- Light sensor and/or potentiometer

- · Seven-segment display or set of LEDs

- 330-Ohm Resistors

- Jumper wires

# 5.3. Background

Many microcontrollers have pins that can be used for *analog input*. Because the microcontroller processes digital data only, analog input must be converted to digital data. An analog-to-digital converter (ADC) is an I/O circuit often integrated into microcontrollers to allow directly connecting external analog devices, such as sensors. The ADC would convert the sensor voltage into a digital value by transforming it into a binary code with a specific number of bits.

Although not critical to conducting this experiment, it would be useful to review the three steps involved in analog-to-digital conversion: sampling, quantization, and bit encoding (COE 241).

### 5.3.1. Using LPC1769 Peripherals

The LPC1769 includes an integrated ADC peripheral device. In general, using any peripheral device involves three main issues:

- 1. Powering up the peripheral

- 2. Configuring the peripheral clock

- 3. Configuring pin functions

#### Power Up

All microcontroller peripherals must be powered up before they can be used. This was not a concern in earlier experiments because we were using peripherals that are powered up by default.

Powering peripherals up and down is controlled through the *Power Control for Peripherals Register* (PCONP).

By referring to table 46 in Chapter 4 of the LPC1769 manual, you can see that the reset value (default value) is 1 for some peripherals, meaning that they are powered on by default, whereas it is 0 (OFF by default) for others.

For example, in the timer experiment, if you use a timer other than timer 0 or timer 1, your experiment wouldn't work without powering up the timer in your program.

The A/D converter (ADC) power is controlled by bit 12 of the PCONP register, which is 0 by default. *You must set that bit to power up your ADC*.

To save power, you can turn the power OFF for any unused peripherals that are ON by default.

#### **Peripheral Clock**

Most of the microcontroller peripherals, including timers and the ADC, require setting a peripheral clock (PCLK) to drive the peripheral.

You have seen in Experiment 7 (Hardware Timers) that you can configure a device's PCLK using the PCLKSEL0 and PCLKSEL1 registers.

#### **Exercise**

Refer to Chapter 4 in the LPC1769 manual to find out the two bits needed to configure the PCLK frequency for the ADC.

#### **Exercise**

What would happen if you skip this step?

#### **Pin Functions**

Many microcontroller pins can be configured to perform one of many functions. From Experiment 3 (Interrupts), recall that the PINSELx registers are used to configure a pin's function. To use the ADC, you must set the function of an appropriate pin to be analog input (ADO.x in the manual).

#### **Exercise**

Refer to Chapter 8 of the LPC176x manual to determine:

- 1. which PINSELx register should be modified

- 2. which bits of the register should be modified

- 3. what value should the bits be set to

You should connect a device that generates an analog voltage signal to the selected pin. Examples of such devices are light sensors (LDR) and potentiometers.

It is professional to correctly address the above three issues for every peripheral you plan to use, regardless of the defaults.

## 5.3.2. ADC Configuration

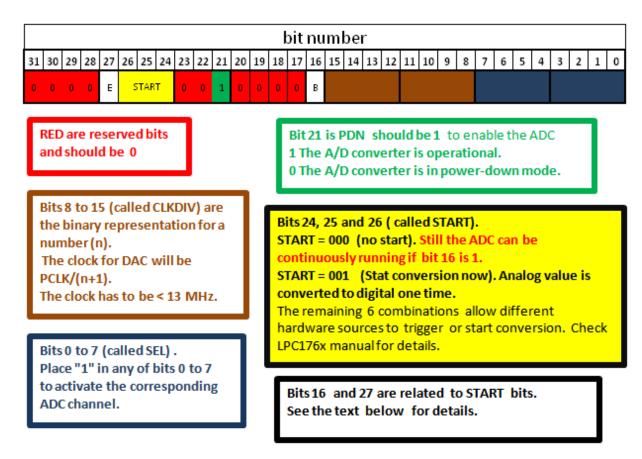

The main setup register for the ADC is the *A/D Control Register* (ADOCR). The ADOCR Register Fields figure illustrates the fields of the ADOCR register.

There is only *one* ADC in the LPC1769 microcontroller. In the LPC17xx.h header file, the control register is referred to as ADCR; while in the chip manual it is called ADOCR. The reason for that is that some other chips have multiple ADCs, named: ADOCR, AD1CR, etc.

Figure 5. A/D Control Register (ADOCR) Fields

The following table explains the function of the B (Burst) and E (Edge) bits of the ADOCR register.

Bit 27 (E) works only if B = 0 and  $START \ge 2$ . When  $2 \le START \le 7$ , the conversion starts when the state of a specific pin is changed. The E bit decides whether the ADC is triggered on the positive edge or the negative edge of that pin specified by START.

| Bit | Label | Value | Effect                                                    |

|-----|-------|-------|-----------------------------------------------------------|

| 16  | В     | 0     | The START bits control when the ADC starts the conversion |

|     |       | 1     | The ADC is continuously running (START should be 000)     |

| 27  | Е     | 0     | Start conversion on a falling edge                        |

|     |       | 1     | Start conversion on a rising edge                         |

### START vs. BURST

Using START will perform the conversion only once.

If you want the analog value to be repeatedly converted, you have two options:

- 1. Set the B bit (Burst) of the ADOCR register to 1; or

- 2. Set the START bits to 001 repeatedly, i.e. in a loop. The analog value is read every time such a statement is executed.

### **Using ADC Interrupt**

In simple ADC applications, you don't need interrupts. You can simply read the digitized value from the proper register whenever needed and take some action. However, in some applications, such as real time

applications, you may need to interrupt the CPU to take an action *only when* the conversion is completed. To do that, you can use the ADGINTEN register.

See Table 534 in Chapter 29 of the LPC1769 manual for details.

# 5.3.3. Reading Digital Values

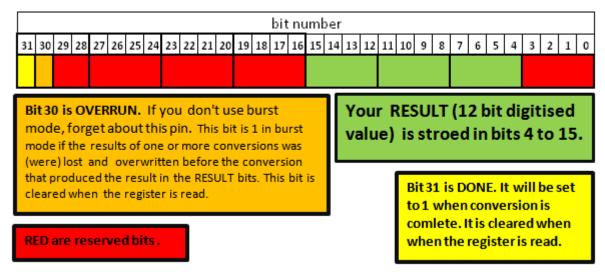

There are 8 ADC channels, each corresponding to an analog pin. The digitized value corresponding to an input analog voltage is stored in 12 bits in one of the *A/D Data Registers*: ADDR0 to ADDR7, where each register corresponds to an analog pin.

The ADDR Register Fields figure illustrates the fields of the ADDRx registers.

Figure 6. A/D Data Register (ADDR) Fields

Using proper shifting and bitwise operations, you should be able to get the proper value representing the analog voltage.

The DONE and OVERRUN bits are less important (may not be needed) in BURST mode. However in START mode, you may need to check them to avoid reading an old or unintended value.

### Example 14. Using the DONE Bit

To wait until the conversion of the ADC channel 3 is over, you may use:

while ((LPC\_ADC->ADDR3 & (1 << 31)) == 0); // Check the DONE bit for ADC channel #3

The 12-bit digital value generated by the ADC ranges from 0 to 4095. The way to process this value depends on your application.

You may want to divide this range to a number of sub-ranges, and assign different actions for each sub-range. In this case, you can use an if-else block.

In many applications, however, you will want to map this range to a another range using a mathematical formula. For example, if you are reading from an analog temperature sensor, you would want to map the 0-to-4095 range to the range of temperatures supported by the sensor, as specified in the sensor's data sheet. In most cases, a linear relationship is sufficient.

# 5.3.4. Analog Output

To write analog values to an analog output device, use the LPC1769's digital-to-analog converter (DAC) as follows:

- 1. Use PINSELx to configure P0.26 to function as analog output (AOUT).

- 2. Use the *D/A Converter Register* (DACR) to set the digital value to be converted to analog.

Refer to Chapter 30 in the LPC1769 manual for details.

# 5.4. Tasks

1. Use the ADC in LPC1769 to read an analog input device, such as the LDR (light sensor) or the potentiometer.

The output can be any thing you want. The seven-segment display is a good option. You can simply display the analog level. If you use one seven-segment display, you have 10 different levels (0 to 9).

It is recommended to use a formula to map the readings to sensible values, instead of using an if-else block.

2. Use the DAC in LPC1769 to output analog values to an analog device.

# 5.5. Resources

[]

NXP Semiconductors. 'UM10360 LPC176x/5x User manual'. Rev. 3.1. 2 April 2014. http://www.nxp.com/documents/user\_manual/UM10360.pdf

# 5.6. Grading Sheet

| Task          | Points |

|---------------|--------|

| Analog Input  | 5      |

| Analog Output | 2      |

| Discussion    | 3      |

# 6. Experiment 6: Pulse-Width Modulation

Hazem Selmi; Ahmad Khayyat 162, 9 April 2017

# 6.1. Objectives

• Understanding and using *pulse-width modulation (PWM)*.

# 6.2. Parts List

- LPC1769 LPCXpresso board

- USB A-Type to Mini-B cable

- Breadboard

- · RGB-LED or buzzer

- · Jumper wires

- · Servo motor

# 6.3. Background

### 6.3.1. Pulse-Width Modulation (PWM)

A pulse-width modulated (PWM) signal is a periodic square wave signal. The difference between a PWM signal and a clock signals is the flexibility of its *duty cycle*.

A periodic square wave is high for some part of its period, and low for the rest of the period. Its *duty cycle* is the percentage of the period for which the signal is high. Usually, a clock wave has a duty cycle of 50%. In a PWM signal, the duty cycle is controllable. The name is derived from the idea that the *width* of the high *pulse* is *modulated* according to some value.

# 6.3.2. PWM Applications

PWM has many useful applications in embedded systems. The main two categories are:

- 1. When a microcontroller does not have a DAC circuit, PWM can be used to *modulate* different analog values.

- 2. Some devices are built to be used with PWM. The most famous example is servo motors.

Servo motors usually require a 50-Hz square wave (period of 20 ms). The duration of the high pulse determines the motor's angle. Usually, the full swing of the servo corresponds to a high interval of 1 to 2 ms, whereas a high interval of 1.5 ms corresponds to the neutral servo position [1: https://circuitdigest.com/article/servo-motor-basics].

# 6.3.3. Generating PWM with LPC1769

The LPC1769 features a pulse-width modulator peripheral. The generic steps discussed in Experiment 5 for setting up a peripheral device apply here:

- 1. Power: the PWM circuit is powered on by default.

- 2. Peripheral Clock (PCLK): recall that the default division factor is 4.

- 3. Pin functions: a PWM pin must be configured for PWM use.

Additionally, generating a PWM signal in particular requires:

- 1. Setting the period of the PWM signal using the MRO register.

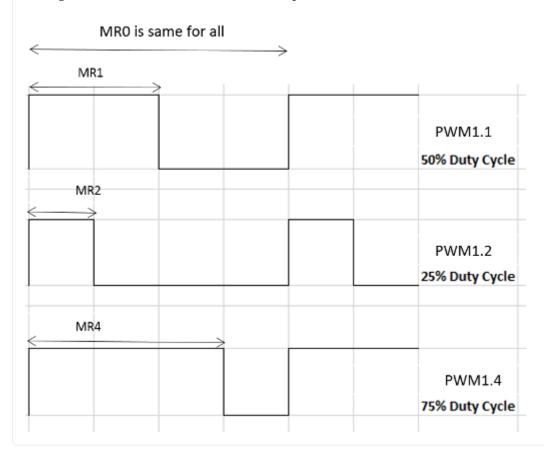

- 2. Specifying the duty cycle using an MRx register, which would control the PWM1.x output.

- 3. The PWM circuit should be enabled to generate a PWM signal, otherwise it will act as a standard timer (or counter).

- 4. The corresponding PWM1.x output should be enabled.

- 1. There is only one PWM circuit, called PWM1. That does not imply that there is a PWM0 or PWM2

- 2. There are six PWM channels, referred to as PWM1.1 to PWM1.6.

- 3. You have the option of more than one pin to pin out any of the channels.

If you care about the accuracy of your PWM output voltage levels, you need to disable the pull-up resistor to avoid affecting the PWM voltage. That can be done using the LPC\_PINCON → PINMODEx register.

In many applications this is not required.

# **Exercise**

Refer to chapter 8 of the LPC176x manual to determine:

- 1. Which pins are you going to use for PWM?

- 2. Which PINSELx register should you use?

- 3. Which PINSELx bits should you set?

- 4. To what value should you set those PINSELx bits?

- 5. How to disable the pull-up resistor?

### MR0 and MRx

To fully specify a PWM signal, you need to specify:

- 1. Its period (or, equivalently, its frequency)

- 2. Its duty cycle

The value of the MR0 register (aka PWM1MR0) determines the period, while any of the MR1 to MR6 registers determine the duty cycle for the corresponding PWM1.1 to PWM1.6 outputs, as illustrated in the following example.