# An All-Digital Clock Frequency Caputring Circuitry For NRZ Data Communications

Muhammad E. S. Elrabaa

Computer Engineering Department King Fahd University of Petroleum and Minerals (KFUPM) Dhahran, Saudi Arabia elrabaa@kfupm.edu.sa

Abstract— A new all-digital circuit scheme for capturing the frequency of an NRZ data stream is described. The proposed scheme is capable of retiming the output clock with the received data within two bit transitions. The absence of analog filters or other analog blocks gives it a much smaller area than conventional circuitry. Also, being fully-digital, it can be described, simulated and synthesized using hardware description languages and be ported to any technology (thus supporting system on a chip designs). Circuit operation and performance was demonstrated using a 0.13 $\mu$ m, 1.2V CMOS technology and T-Spice® simulations.

#### I. INTRODUCTION

Serial data communications have become the standard de-facto due to the high achievable data rates and reliability. Applications range from backplane communications, to fiber data transmission. Also, as the interconnect technology moves from bus-based schemes to switch/router based schemes, the demand for low overhead, low-power and portable serial communication circuits is ever increasing.

A crucial part of non return-to-zero (NRZ) serial communication is the clock recovery and data retiming circuitry. These circuits, setting in the repeaters and receivers, accurately extract clock signals from non return-to-zero (NRZ) serial bit streams. They must maintain synchronism between the generated clock and the data in the presence of data phase noise (jitter), supply and temperature fluctuations. Also, they must be agile in extracting synchronized clocks for different data packets arriving from different sources.

The job of clock recover circuits is further made difficult due to the nature of random NRZ data; they have no spectral contents at the bit rate or its even-order harmonics [1, 2]. This problem can be circumvented using edge detection techniques. Also, long streams of consecutive 1s and 0s represent a serious problem to traditional clock recovery circuits that utilize Phase-Locked-Loops (PLLs) and result in data-dependent jitter in the PLL's output. To reduce this jitter the PLL's bandwidth has to be limited which in turn

limits the PLL's capture range. Also, larger loop gain reduces jitter generation but reduces stability.

Analog PLLs suffer from several shortcomings; large area (due to analog blocks), difficulty to port to other processes or supplies, high VCO operating frequency (double the data frequency) which in turn limits the data rate, phase error accumulation in the VCO, and long lock times due to the loop damping behavior.

Fully digital or semi-digital solutions were proposed to solve some of the analog PLLs problems [3-6]. Though these techniques retain many of the analog features, they suffer from poor resolution (more jitter), stability issues (two or more loops interacting), difficulty to port from one process to another (due to analog blocks) and/or large areas. A fully digital non PLL/DLL technique for source synchronous serial communication (clock frequency available, but the phase its needs re-timing) demonstrated the potential of digital circuits in clock recovery and data re-timing [7]. In this work a novel non PLL/DLL digital technique for clock recovery and re-timing is introduced. The clock frequency is captured from the NRZ data stream and is aligned with the data. The circuit retimes the clock with each data transition.

The basic operation and circuit description of the proposed clock-frequency capturing circuit (CFCC) are given in section 2. Performance evaluations are presented in section 3 followed by conclusions in section 4.

## II. THE PROPOSED CFCC

# A. Basic Concept of Operation

The basic idea of the CFCC circuit is to use a variable length digital delay line to measure the input data's bit duration (i.e. the time between a positive edge and a negative edge). This delay is then used in a feedback loop to form an oscillator with an oscillation period equal to that delay (i.e. the oscillation frequency will be twice the maximum data rate).

This research project has been funded by King Fahd University of Petroleum & Minerals under project # COE/DIGITAL/287.

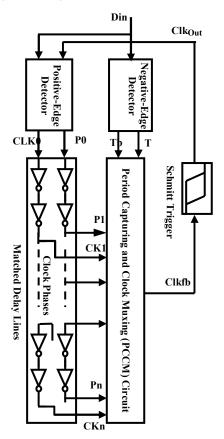

The architecture of the proposed CFCC is shown in Figure 1. When the incoming NRZ data (Din) exhibits a positive transition  $(0 \rightarrow 1)$ , the positive-edge detector (**PED**) circuit produces a pulse (P<sub>0</sub>) that would travel down a delay line. The delay line will provide several phases of this pulse  $(P_1 \text{ to } P_n)$ . An identical delay line will also contain a replica of this pulse, providing unloaded clock phases (CLK0 to  $CLK_n$ ). When the next negative NRZ data edge arrives, the negative-edge detector (NED) circuit will generate two complementary pulses, T and T<sub>b</sub>, which will be used to latch in the appropriate pulse phase. This latched pulse phase is then used as an enable signal for a mux to select the corresponding clock phase. More than one clock phase might be selected, making the resulting feedback clock (Clk<sub>fb</sub>) an interpolated version of the selected clock phases, enhancing the CFCC's resolution significantly. This feedback clock is then re-constructed using a simple Schmitt Trigger before it is fed back to the **PED** circuit. This closes the loop and forms a ring oscillator with a total delay of 1 bit duration (i.e. bit cell).

Figure 1. The architecture of the proposed clock-frequency capturing circuit (CFCC).

The CFCC will oscillate at twice the input's frequency and from this point onward it will continue to oscillate even with the absence of any positive or negative input data edges. With each data transition the circuit re-times the clock with data, hence correct for any injected phase and/or frequency noise.

# B. Circuit Description

The proposed CFCC circuit has five main components; a positive-edge detector circuit (**PED**), a negative-edge detector circuit (**NED**), two delay lines, a period capturing and clock muxing (**PCCM**) circuit, and a Schmitt Trigger. All blocks are implemented using standard CMOS circuits.

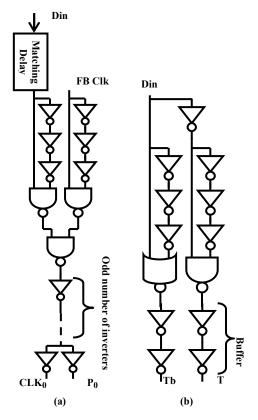

Figure 2 shows the schematics of the PED and NED circuits. The **PED** circuit (Figure 2 (a)) generates narrow output pulses for every positive transition in the NRZ input data or feedback clock. The output pulses have a width of 3 inverter's delay. Adding more inverters in the second input path of the NAND gates can increase the width of the output pulses. These pulses are used to re-synchronize the output clock of the CRC with the input data (in the absence of data transitions the output clock will remain at the same frequency and phase). An odd number of inverters are used to delay these pulses by a fixed delay. The amount of required delay depends on the intended range of data frequencies.

The **NED** circuit is similar to the PED except that it generates 2 complementary output pulses (T and Tb) only when the input data exhibits a negative transition. These pulses are used by the PCCM circuit to latch the appropriate phase(s) of the clock pulse (from CK0 to CKn). The matching delay matches the delay of PCCM and Schmitt trigger circuits.

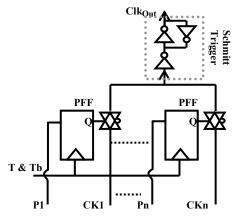

Figure 3 shows the circuit diagram of the period capturing and clock muxing circuit along with the simple Schmitt trigger used. The basic block is a pulsed flip-flop (PFF) whose inputs come from one of the identical delay lines and are triggered by the complementary pulses T and Tb. The output of each PFF controls a transmission gate. When a clock pulse coincides with T and Tb, the PFF will latch a 1 and hence turn on the corresponding transmission gate which will connect the selected clock phase (from the second delay line) to the output. The delay lines are made of simple CMOS inverters.

The total number of gates in the CFCC is less than 100, most of which are inverters. This makes the circuit very compact allowing the instantiation of many copies for different serial links within the same chip.

### III. PERFORMANCE EVALUATION

Circuit simulations using T-Spice and a  $0.13\mu m$ , 1.2V CMOS technology were used to evaluate the operation and performance of the proposed circuit. Sizes of transistors in the circuit components were optimized for 2 GBPS operation, but it can still operate with any input frequency up

to 2.5 GBPS. For lower frequencies the fixed delay in the PED circuit is increased keeping the ELCM circuit the same.

Figure 2. (a) The positive-edge detector circuit, (b) The negative-edge detector.

Figure 3. The PCCM Circuit's Schematic including the Schmitt Trigger.

#### A. Basic Operation

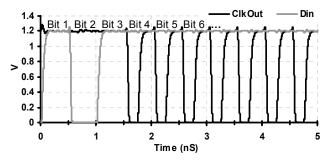

Figure 4 below shows how the CFCC captures the data frequency at 2 GBPS and generates an output clock after two bit transitions. The data pattern used was 1011111111.

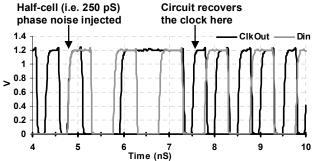

Figure 5 shows how the circuit fully recovers the clock within two data transitions after a large phase noise

(equivalent to a half bit cell) is injected into the input data. An analog PLL would have taken hundreds or even thousands of cycles to recover.

Figure 4. The output clock waveform at 2 GBPS.

Figure 5. Output clock recovery after the injection of a large phase noise (half-cell) at 2 GBPS.

# B. Stability of Output Frequency

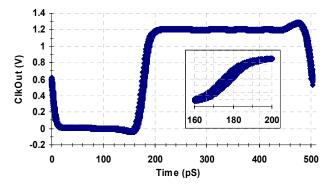

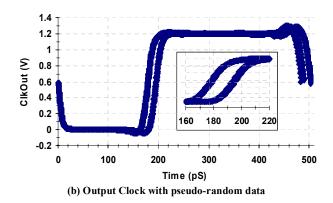

A major concern of using a digital circuit in clock recovery might arise; that is the stability of the output frequency. To evaluate the stability of the output clock's frequency, two simulations were carried out; one with no data transitions after the initial clock frequency capturing (i.e. data stays constant after the two initial bit transitions) and another with a pseudo-random input stream (using 6-bit long pseudo-random patterns that are fed serially to the circuit). The output clock periods were laid out on top of one another in Figure 6 (a) and (b).

As this figure shows, the peak-to-peak period jitter in the case of no data transitions is less than 10 pS. This is an outstanding performance for an all-digital clock recovery circuitry. The results in Figure 6(b) show that the output clock has two modes with about 10 pS difference in their periods. The peak-to-peak period jitter within each mode is still less than 10 pS. These two modes result from variations in the loop delay due to two modes of operation; when there is no positive data transition and when there is such transition. As Figure 2(a) shows, the delay of the PED circuit is slightly smaller when there is a positive input data transition (since in this case both inputs to the second NAND gate are going high). This bi-modal operation of the CFCC won't cause bit errors since the faster mode only occur when there is an input transition and the circuit immediately goes back to the normal mode when there is no data transitions (i.e. there is no accumulation of phase error). It should be noted that the relative difference between the two modes will be smaller for lower clock frequencies.

(a) Output Clock with no data transitions after the first two

Figure 6. Output Clocks laid on top of one another. The insets show a Zoom-in of clock edge region.

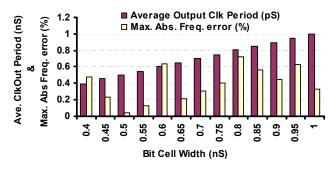

Figure 7 shows the average output clock period for different data rates. The circuit components were only optimized once for the 2 GBPS data rate (0.5 nS bit cell). For other data rates, only the fixed delay part of the PED circuit was changed (by changing the number of inverters at its output). As the results in the figure indicate, the maximum frequency error is still below 0.8% for other data rates. The accumulated phase error due to the frequency error, however, is reset with every time a data transition occurs. This means that with proper data encoding that ensure adequate data transitions, the bit error rate can be set to a desired value.

## IV. CONCLUSIONS

An all-digital clock-frequency capturing circuit has been developed. The proposed circuit can capture the clock frequency of an NRZ data stream within two bit transitions.

Simulation results show that the output clock frequency of the circuit is very stable. Output frequency error could be made very small by proper sizing of the circuit components for the intended technology. However, the circuit continuously re-times the clock phase with each bit transition. This means that with adequate data encoding the impact of frequency error on bit error rate can be virtually eliminated. The circuit has less than 100 gates (most of which are inverters). This makes it very compact, highly portable and can support SoC designs with many serial links.

Figure 7. The average output clock Frequency and maximum absolute frequency error for different data rates.

#### REFERENCES

- B. Razavi, "A 2.5-Gb/s 15-mW Clock Recovery Circuit," IEEE JSSC, Vol. 31-4, pp. 472-480, 1996.

- [2] S. Anand and B. Razavi, "A CMOS Clock Recovery Circuit for 2.5-Gb/s NRZ Data," IEEE JSSC, Vol. 36-3, pp. 432-439, 2001.

- [3] D-L. Chen, "A Power and Area Efficient CMOS Clock/Data Recovery Circuit for High-Speed Serial Interfaces," IEEE Journal of Solid-State Circuits, Vol. 31, No. 8, pp. 1170-1176, August 1996.

- [4] T. Saeki et al., "A 1.3-Cycle Lock Time, Non-PLL/DLL Clock Multiplier Based on Direct Clock Cycle Interpolation for Clock on Demand," IEEE Journal of Solid-State Circuits, Vol. 35, No. 11, pp. 1581-1590, November 2000.

- [5] T-Y. Hsu et al., "An All-Digital Phase-Locked Loop (ADPLL)-Based Clock Recovery Circuit," IEEE JSSC, Vol. 34-8, pp. 1063-1073, 1999

- [6] M. Combes et al., "A Portable Clock Multiplier Generator Using Digital CMOS Standard Cells," IEEE JSSC, Vol. 31-7, pp. 958-965, 1996.

- [7] M. E. S. Elrabaa, "An All-Digital Clock Recovery and Data Retiming Circuitry for High Speed NRZ Data Communications," Institute of Electronics, Information and Communication Engineers (Japan) Transactions on Electronics, Vol. E85-C, No. 5, P. 1170, May 2002.