|        |                  |                                  |        |     |     | יפי | nals -                          | con      | <u> </u> |                     |

|--------|------------------|----------------------------------|--------|-----|-----|-----|---------------------------------|----------|----------|---------------------|

| Ор     | Decode<br>Signal | Execute Stage<br>Control Signals |        |     |     |     | Memory Stage<br>Control Signals |          |          | Writeback<br>Signal |

|        | RegDst           | ALUSrc                           | ALUOp  | Beq | Bne | j   | MemRead                         | MemWrite | MemtoReg | RegWrite            |

| R-Type | 1=Rd             | 0=Reg                            | R-Type | 0   | 0   | 0   | 0                               | 0        | 0        | 1                   |

| addi   | 0=Rt             | 1=lmm                            | ADD    | 0   | 0   | 0   | 0                               | 0        | 0        | 1                   |

| slti   | 0=Rt             | 1=lmm                            | SLT    | 0   | 0   | 0   | 0                               | 0        | 0        | 1                   |

| andi   | 0=Rt             | 1=lmm                            | AND    | 0   | 0   | 0   | 0                               | 0        | 0        | 1                   |

| ori    | 0=Rt             | 1=lmm                            | OR     | 0   | 0   | 0   | 0                               | 0        | 0        | 1                   |

| lw     | 0=Rt             | 1=lmm                            | ADD    | 0   | 0   | 0   | 1                               | 0        | 1        | 1                   |

| SW     | x                | 1=lmm                            | ADD    | 0   | 0   | 0   | 0                               | 1        | x        | 0                   |

| beq    | x                | 0=Reg                            | SUB    | 1   | 0   | 0   | 0                               | 0        | x        | 0                   |

| bne    | x                | 0=Reg                            | SUB    | 0   | 1   | 0   | 0                               | 0        | x        | 0                   |

| i      | x                | x                                | х      | 0   | 0   | 1   | 0                               | 0        | х        | 0                   |

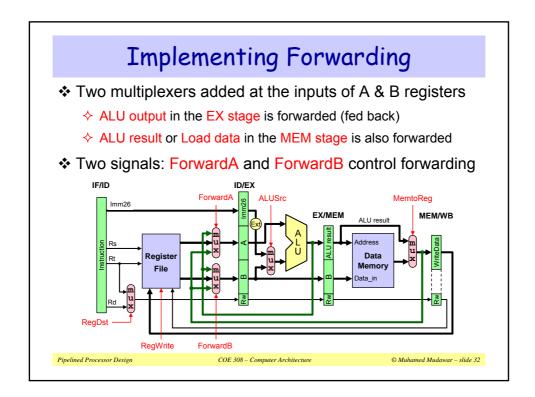

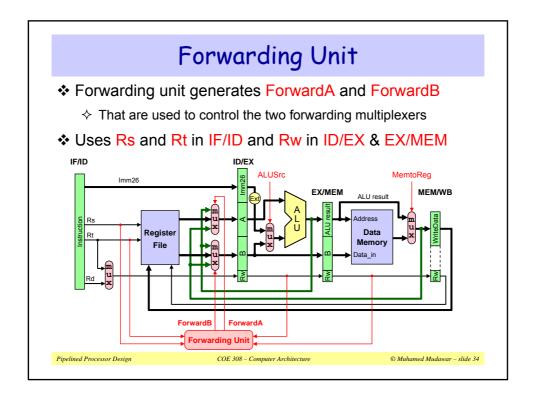

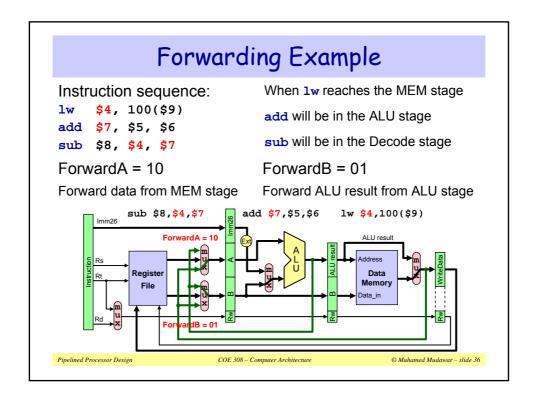

| Forwarding Control Signals |                                                                   |  |  |  |  |  |

|----------------------------|-------------------------------------------------------------------|--|--|--|--|--|

| Control Signal             | Explanation                                                       |  |  |  |  |  |

| ForwardA = 00              | First ALU operand comes from the register file                    |  |  |  |  |  |

| ForwardA = 01              | Forwarded from the previous ALU result                            |  |  |  |  |  |

| ForwardA = 10              | Forwarded from data memory or 2 <sup>nd</sup> previous ALU result |  |  |  |  |  |

| ForwardB = 00              | Second ALU operand comes from the register file                   |  |  |  |  |  |

| ForwardB = 01              | Forwarded from the previous ALU result                            |  |  |  |  |  |

| ForwardB = 10              | Forwarded from data memory or 2 <sup>nd</sup> previous ALU result |  |  |  |  |  |

| if (IF/ID.Rs =             | == ID/EX.Rw≠0 and ID/EX.RegWrite) ForwardA = 0                    |  |  |  |  |  |

| elseif (IF/ID.Rs =         | == EX/MEM.Rw ≠ 0 and EX/MEM.RegWrite) ForwardA = 10               |  |  |  |  |  |

| else ForwardA =            | : 00                                                              |  |  |  |  |  |

| if (IF/ID.Rt =             | == ID/EX.Rw≠0 and ID/EX.RegWrite) ForwardB = 01                   |  |  |  |  |  |

| elseif (IF/ID.Rt =         | = EX/MEM.Rw≠0 and EX/MEM.RegWrite) ForwardB = 10                  |  |  |  |  |  |

| else ForwardB =            | 00                                                                |  |  |  |  |  |

| Pipelined Processor Design | COE 308 – Computer Architecture © Muhamed Mudawar – slide 35      |  |  |  |  |  |

|                           | Comp                          | iler Schedu                     | lling  | 9                             |  |  |

|---------------------------|-------------------------------|---------------------------------|--------|-------------------------------|--|--|

| <ul> <li>Compi</li> </ul> | lers can scheo                | dule code in a way              | y to a | void load stalls              |  |  |

| ✤ Consid                  | ler the followir              | ng statements:                  |        |                               |  |  |

| a = b                     | ) + c; d = e - f;             |                                 |        |                               |  |  |

| Slow c                    | ode:                          | Fast code: No Stalls            |        |                               |  |  |

| lw                        | \$10, (\$1)                   | # \$1 = addr b                  | lw     | \$10, 0(\$1)                  |  |  |

| lw                        | <mark>\$11</mark> , (\$2)     | # \$2 = addr c                  | lw     | <mark>\$11</mark> , 0(\$2)    |  |  |

| add                       | \$12, \$10, <mark>\$11</mark> | # stall                         | lw     | \$13, 0(\$4)                  |  |  |

| SW                        | \$12, (\$3)                   | #\$3 = addr a                   | lw     | <mark>\$14</mark> , 0(\$5)    |  |  |

| lw                        | \$13, (\$4)                   | #\$4 = addr e                   | add    | \$12, \$10, <mark>\$11</mark> |  |  |

| lw                        | <mark>\$14</mark> , (\$5)     | # \$5 = addr f 🦯                | SW     | \$12, 0(\$3)                  |  |  |

| sub                       | \$15, \$13, <mark>\$14</mark> | # stall                         | sub    | \$15, \$13, <mark>\$14</mark> |  |  |

| SW                        | \$15, (\$6)                   | # \$6 = addr d                  | SW     | \$14, 0(\$6)                  |  |  |

| Pipelined Processor D     | esign                         | COE 308 – Computer Architecture |        | © Muhamed Mudawar – slide 42  |  |  |