#### **INFORMATION TO USERS**

This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps. Each original is also photographed in one exposure and is included in reduced form at the back of the book.

Photographs included in the original manuscript have been reproduced xerographically in this copy. Higher quality 6" x 9" black and white photographic prints are available for any photographs or illustrations appearing in this copy for an additional charge. Contact UMI directly to order.

UMI

A Bell & Howell Information Company 300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA 313/761-4700 800/521-0600

|  | • |  |

|--|---|--|

|  |   |  |

|  |   |  |

# **Intermediate Forms in High-Level Synthesis**

Essam Mohammad Khair Hubbi

A Thesis Presented to the FACULTY OF THE COLLEGE OF GRADUATE STUDIES

KING FAHD UNIVERSITY OF PETROLEUM & MINERALS

DHAHRAN, SAUDI ARABIA

In Partial Fulfillment of the Requirements for the Degree of

MASTER OF SCIENCE In Computer Engineering

November 1994

UMI Number: 1361060

UMI Microform Edition 1361060 Copyright 1995, by UMI Company. All rights reserved.

This microform edition is protected against unauthorized copying under Title 17, United States Code.

UMI

300 North Zeeb Road Ann Arbor, MI 48103

#### KING FAHD UNIVERSITY OF PETROLEUM AND MINERALS DHAHRAN 31261, SAUDI ARABIA COLLEGE OF GRADUATE STUDIES

This thesis, written by

#### Essam Mohammad Khair Hubbi

under the direction of his thesis advisor and approved by his thesis committee, has been presented to and accepted by the Dean of the College of Graduate Studies, in partial fulfillment of the requirements for the degree of

#### MASTER OF SCIENCE IN COMPUTER ENGINEERING

Thesis Committee:

Jadiq Sait. M.

Dr. Sadiq M. Sait (Chairman)

Sur But 11

Dr. Muhammad S. T. Benten (Member)

Department Chairman

Dean College of Graduate Studies

Data

Date

To my family

whose support and prayers

led to this achievement.

#### Acknowledgments

٠:.

All praise be to Allah for his limitless help and guidance. Peace and blessings of Allah be upon his prophet Mohammad.

Acknowledgement is due to King Fahd University of Petroleum and Minerals, Dhahran, Saudi Arabia, for the generous help and support for this research.

I would like to express my profound appreciation to my advisor, Dr. Sadiq M. Sait, Associate Professor of Computer Engineering, for his guidance and patience throughout this thesis.

I would also like to thank co-chairman, Dr. Habib Youssef Assistant Professor of Computer Engineering, whose continuous encouragement can never be forgotten, and Dr. Muhammad S. T. Benten, Associate Professor of Computer Engineering for his consistent support and valuable suggestions. I also wish to thank faculty, research assistants, graduate assistants, and the staff members of the Computer Engineering Department for their support.

The encouragement and good wishes of the following friends in CCSE and other departments is also worthy of acknowledgement. They are: Hazem Abu-Saleh and Saleh Al-Meshari.

Finally, special thanks must be given to my family for their encouragement and moral support.

# Contents

|   | Ack  | nowled  | gment                                                    |   | i    |

|---|------|---------|----------------------------------------------------------|---|------|

|   | List | of Fig  | ures                                                     |   | v    |

|   | List | of Tab  | oles                                                     | V | riii |

|   | Abs  | tract ( | English)                                                 |   | ix   |

|   | Abs  | tract ( | Arabic)                                                  |   | x    |

| 1 | Intr | oducti  | o <b>n</b>                                               |   | 1    |

|   | 1.1  | Definit | ion of High-level Synthesis                              | • | 4    |

|   |      | 1.1.1   | Date Flow Graph (DFG)                                    | • | 5    |

|   |      | 1.1.2   |                                                          |   | 7    |

|   |      | 1.1.3   | Control-Data Flow Graph (CDFG)                           | • | 7    |

|   | 1.2  | The M   | lain Tasks in HLS                                        | • | 13   |

|   |      | 1.2.1   | Transformation                                           | • | 14   |

|   |      | 1.2.2   | Scheduling                                               | • | 14   |

|   |      | 1.2.3   | Allocation and Module Binding                            |   |      |

|   |      | 1.2.4   | Control Path Synthesis and Merging Data and Control Path | • | 16   |

| 2 | Inte | ermedi  | ate Forms and High-Level Synthesis Tasks                 |   | 17   |

|   | 2.1  | Intern  | nediate Forms Used in Transformation                     | • | 18   |

|   |      | 2.1.1   | Transformation in HARP                                   |   |      |

|   |      | 2.1.2   |                                                          |   | 22   |

|   |      | 2.1.3   | Transformation in HAL                                    |   | 24   |

|   |      | 2.1.4   | Summary                                                  |   | 24   |

|   | 2.2  | Intern  | nediate Forms Used in Scheduling                         |   | 27   |

|   |      | 2.2.1   | ASAP and ALAP Scheduling                                 |   | 28   |

|   |      | 2.2.2   | Force-Directed Scheduling in HAL                         |   | 28   |

|   |      | 2.2.3   | Path-Based Scheduling                                    |   | 35   |

|   |      | 2.2.4   | Summary                                                  |   | 38   |

|   | 2.3  | Intermediate Forms Used During Allocation              | <b>39</b>       |

|---|------|--------------------------------------------------------|-----------------|

|   |      | 2.3.1 Allocation in FACET Synthesis System             | 39              |

|   |      | 2.3.2 Allocation in HARP                               | 46              |

|   |      | 2.3.3 Discussion                                       | <b>52</b>       |

|   | 2.4  | Conclusion                                             | 53              |

| 3 | Clas | ssification of Intermediate Forms                      | 55              |

| • | 3.1  | Constraints                                            | 55              |

|   | 3.2  | Classes of Intermediate Forms                          |                 |

|   | 3.3  | HAL Synthesis System                                   | 57              |

|   | 3.4  | FACET Synthesis System                                 | 60              |

|   | 3.5  | HARP Synthesis System                                  | 61              |

|   | 3.6  | Path-Based Synthesis System [3]                        | 63              |

|   | 3.7  | Conclusion                                             | 65              |

|   |      |                                                        | 67              |

| 4 |      | neric Intermediate Form                                | <b>67</b><br>68 |

|   | 4.1  | Introduction and Definition                            | 70              |

|   | 4.2  | Generic Control-Data Flow Graph (GCDFG) Transformation | -               |

|   |      | 4.2.1 Transforming Blocks                              | 70              |

|   |      | 4.2.2 Transforming Control Constructs                  | 74              |

|   |      | 4.2.3 Hierarchy                                        |                 |

| • | •    | 4.2.4 Arrays                                           | 81              |

|   | 4.3  | Complexity Analysis                                    | 83              |

|   |      | 4.3.1 Space Complexity                                 | 84              |

|   |      | 4.3.2 Derivation Complexity                            | 86              |

|   | 4.4  | GCD Example                                            | 80              |

|   | 4.5  | Optimization                                           | 93              |

|   | 4.6  | Scheduling and Allocation Example                      | 95              |

|   |      | 4.6.1 Transformation                                   | 99              |

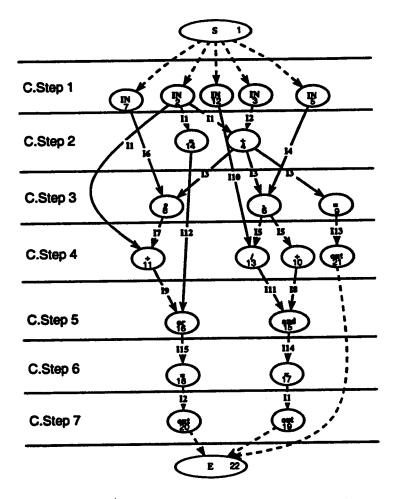

|   |      | 4.6.2 Scheduling                                       | 102             |

|   |      | 4.6.3 Allocation                                       | 103             |

|   | 4.7  |                                                        | 107             |

|   | 4.8  | Conclusion                                             | . 108           |

| 5 | Co   | omparative Study of Flow Graphs                        | 115             |

| _ | 5.1  | Value Trace (VT)                                       | . 116           |

|   |      | 5.1.1 The MIN example                                  | . 118           |

|   | 5.2  | SALSA                                                  | . 124           |

|   | 5.3  | Exchange DFG                                           | . 127           |

|   | 5.4  | Generic CDFG                                           | . 127           |

| e | S Co | onclusion and Future Work                              | 131             |

| Bibliography | 134 |

|--------------|-----|

| Vita         | 137 |

# List of Figures

| 1.1  | Synthesis levels and silicon compiler                                | 2    |

|------|----------------------------------------------------------------------|------|

| 1.2  | Digital system representation. (a) Behavioral level. (b) Structural  |      |

|      | level                                                                | 4    |

| 1.3  | Data flow graph                                                      | 6    |

| 1.4  | The CFG and the DFG representing an if-then-else statement           | 8    |

| 1.5  | The CFG and the DFG representing a while loop                        | 8    |

| 1.6  | IN, OUT and constant nodes                                           | 10   |

| 1.7  | If-then-else construct                                               | 11   |

| 1.8  | While loop with Entry and Exit nodes                                 | 11   |

| 1.9  | Example of Get and Put nodes                                         | 12   |

| 1.10 | Array example                                                        | 13   |

| 2.1  | High-level specification (basic block).                              | 20   |

| 2.1  | The corresponding DFG of the FORTRAN code of Figure 2.1              |      |

| 2.2  | Parallel code reconstructed from the DFG of Figure 2.2               | 22   |

|      | The corresponding DFG of the FORTRAN code of Figure 2.1              |      |

| 2.4  | Combined Control and Data Flow Graph                                 | 25   |

| 2.5  | (a) ASAP scheduling. (b) ALAP scheduling                             |      |

| 2.6  | Time frames and distribution graph. (a) For multiply operation. (b)  |      |

| 2.7  | For add, subtract and compare operations                             | 30   |

|      | Final time frames and distribution graph.                            |      |

| 2.8  | Behavioral description with an if statement and the corresponding:   |      |

| 2.9  | (a) CDFG. (b) Time frames. (c) DG                                    | . 34 |

|      |                                                                      |      |

| 2.10 | Behavioral description of an instruction fetch unit for a micro-pro- | . 35 |

|      | cessor, and the corresponding CFG.                                   |      |

| 2.11 | Constraints and interval graph.                                      |      |

|      | 2 The control finite state machine                                   |      |

| 2.13 | 3 A code sequence                                                    |      |

| 2.14 | The edge list of the compatible variable graph.                      |      |

| 2.1  | The edge list of the FUs compatible graph                            |      |

| 2.10 | The edge list of the interconnections compatible graph               |      |

| 2.17 | 7 Initial schedule for the FORTRAN code of Figure 2.1                | . 41 |

| 2.18 | Final schedule and the allocated ALUs                                | 50    |

|------|----------------------------------------------------------------------|-------|

| 3.1  | HAL high-level synthesis system.                                     | 59    |

| 3.2  | HARP high-level synthesis system.                                    | 62    |

| 3.3  | Path-based high-level synthesis system                               | 64    |

| 4.1  | Blocks in: (a) while loop (b) if-then-else statement                 | 70    |

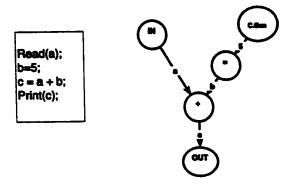

| 4.2  | The GCDFG of $c=a+b$                                                 |       |

| 4.3  | FORTRAN code                                                         | 72    |

| 4.4  | A GCDFG of the basic block in Figure 4.3                             | 73    |

| 4.5  | Parallel FORTRAN code as per the GCDFG in Figure 4.4                 | 74    |

| 4.6  | The GCDFG of a for loop                                              | 76    |

| 4.7  | The GCDFG of a while loop                                            | 77    |

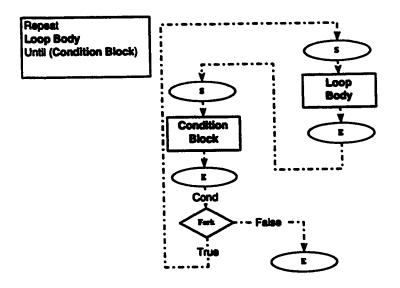

| 4.8  | The GCDFG of a general repeat-until loop                             | 78    |

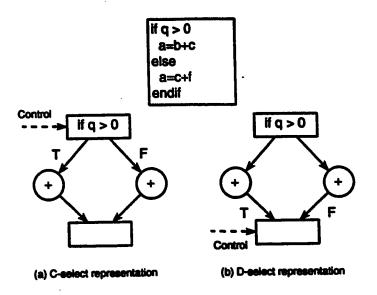

| 4.9  | Conditional representation                                           | 79    |

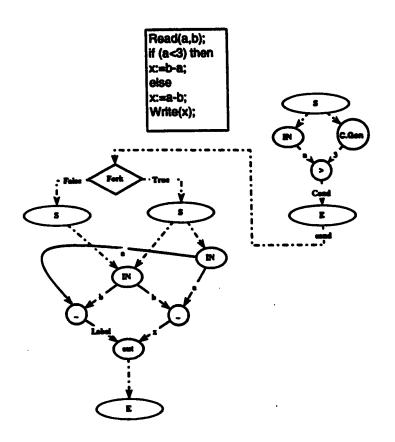

| 4.10 | A GCDFG of an if-then-else statement                                 | 80    |

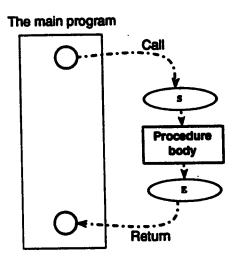

| 4.11 | A procedure call                                                     | 81    |

| 4.12 | (a) The GCDFG for write to array operation. (b) The GCDFG for        |       |

|      | read from array operation.                                           | . 82  |

| 4.13 | This algorithm parses the input and creates the node-list and edge-  |       |

|      | list, (continued. next page)                                         | 87    |

| 4.14 | The parsing algorithm (continued from Figure 4.13)                   | . 88  |

| 4.15 | The parsing algorithm, (continued from Figure 4.14)                  | . 89  |

| 4.16 | A behavioral specification fragment in VHDL                          | . 90  |

| 4.17 | The GCDFG of the VHDL behavioral specification of Figure 4.16.       | . 91  |

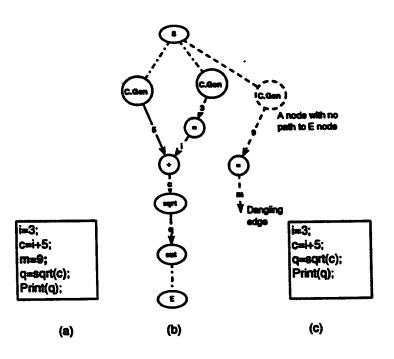

| 4.18 | High-level optimization: (a) High-level code with useless statement. |       |

|      | (b) The corresponding GCDFG and the dangling edge. (c) The high-     |       |

|      | level code after eliminating useless statements                      | . 98  |

| 4.19 | 9 Useless code detection and elimination algorithm                   | . 98  |

| 4.2  | O An ASAP schedule of the GCDFG of the behavior in Figure 4.3.       | . 102 |

| 4.2  | 1 ASAP scheduling algorithm.                                         | . 103 |

| 4.2  | 2 Algorithm for constructing life-time table from GCDFG              | . 106 |

| 4.2  | 3 The format of the GCD-List ASCII file                              | . 109 |

| 4.2  | 4 An example of a GCD-List ASCII file                                | . 110 |

| 4.2  | 5 Example of GCD-List file (continued)                               | . 111 |

| 4.2  | 6 Example of GCD-List file (continued)                               | . 112 |

| 4.2  | 7 A part of the GCD-List file showing constraints                    | . 113 |

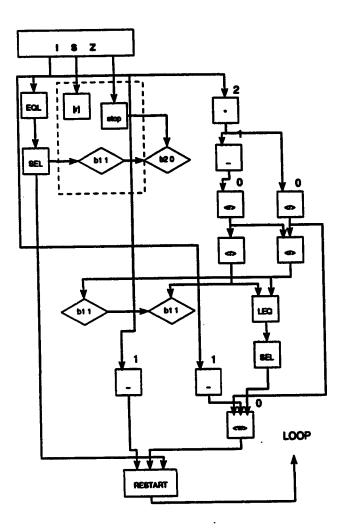

| 5.1  | ISPS of MIN [17]                                                     | . 119 |

| 5.2  | VT representation of the MIN example of Figure 5.1                   | . 120 |

| 5.3  | The Value Trace of the MIN example of Figure 5.1                     | . 12  |

| 5.4  |                                                                      | . 12  |

| 5.5 | The Value Trace of MIN (Continued from 5.4) |

|-----|---------------------------------------------|

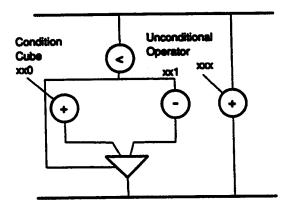

|     | Conditional operations in SALSA             |

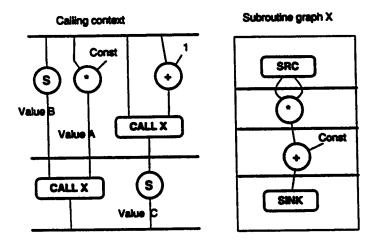

|     | Subroutines in SALSA                        |

··..

# List of Tables

| 2.1  | High-level languages and their supporting features    |

|------|-------------------------------------------------------|

| 2.2  | Intermediate forms and their supporting constructs 27 |

| 2.3  | Intermediate forms and scheduling techniques          |

| 2.4  | Life-time table                                       |

| 2.5  | Indices of interconnections                           |

| 2.6  | Used/unused matrix                                    |

| 2.7  | Restriction database                                  |

| 2.8  | Mutual correlation matrix                             |

| 2.9  | Definition and reference history                      |

| 2.10 | Preliminary life-time table                           |

| 2.11 | Final life-time table                                 |

| 3.1  | Primary and secondary intermediate forms              |

| 4.1  | The node-list                                         |

| 4.2  | Continued, the node-list                              |

| 4.3  | The edge-list, continued in the next page             |

| 4.4  | Continued the edge-list                               |

| 4.5  | The node-list                                         |

| 4.6  | The edges-list                                        |

| 4.7  | The scheduled GCDFG                                   |

| 4.8  | Lifetime table                                        |

| 5.1  |                                                       |

#### Abstract

Name:

Essam Mohammad Khair Hubbi.

Title:

Intermediate Forms in High-Level Synthesis.

Major Field:

Computer Engineering.

Date of Degree:

November, 1994.

High-level synthesis (HLS) is the automatic translation of a behavioral description into a structural description. This translation process is very complicated, therefore, it is broken into several tasks. Each task is performed with the help of some intermediate forms. In this work, a survey of various intermediate forms used in known high-level synthesis systems is introduced. Then, a classification framework that classifies intermediate forms into two main classes (primary and secondary) is introduced. After that, essential and desirable features of primary intermediate forms are identified. Finally, a new primary intermediate form called the Generic Control-Data Flow Graph (GCDFG) and its GCD-List notation are introduced. This GCDFG has all the desirable features of primary intermediate forms and facilitates synthesis tasks like scheduling and allocation. This GCDFG is expressed in the GCD-List notation which has a lisp-like format. This makes it rich and flexible format since attributes can be easily added and hence more constraints can be accomodated. Moreover, it is stored in ASCII text format which makes it portable and machine processible.

Master of Science Degree

King Fahd University of Petroleum and Minerals

Dhahran, Saudi Arabia

November, 1994

### الخلاصة

عصام محمد خير حبي. الصيغ الوسيطية في التصميم عالى المستوى.

العنوان: التخصص:

الإسم:

هندسة حاسب ألي. نوفمبر ١٩٩٤ م.

تاريخ منع الدرجة:

التصميم عالى المستوى هو عملية التحويل الألى للمواصفات العامة لسلوكيات الدوائسر المتكاملة إلى التصميم التركيبي لتلك الدوائر. و لأن عملية التصميم عالى المستوى عملية معقدة، فإنه يتم تقسيم هذه العملية إلى عدد من المراحل. و تقوم هذه المراحل مجتمعة بعملية التحويل بالإستعانة ببعض الصيغ الوسيطية.

يقوم هذا البحث بدراسة عدد من الصيغ الوسيطية في أنظمة التصميم عالى المستوى المعروفة. كما يقوم هذا البحث بوضع إطار تصنيفي تصنف على أساسه هذه الصيغ الوسيطية إلى صنفين (أساسية و ثانوية). كما يتم التعرف على السمات الضرورية و الإضافية للصيغ الوسيطية الأساسية.

كما يقدم هذا البحث صيغة وسيطية أساسية مبتكرة تسمى رسم إنسياب بيانات التحكم العام تخزن على شكل لغة تسمى لائحة إنسياب بيانات التحكم العامة. و تشبة لائحة إنسياب بيانات التحكم العامة إلى حد كبير لغة "ليسب" مما يجعلها لغة غنية و مرنة ومساعدة في مراحل التصميم عالى المستوى المختلفة مثل: جدولة العمليات و توزيع المكونات. بالإضافة إلى كل ماذكر تخزن لائحة إنسياب بيانات التحكم العامة بشكل نصبي مما يجعلها سهلة النسخ و النقل و قابلة المعالجة الألدة.

ماجستير في علوم هندسة الحاسب الألي جامعة الملك فهد للبترول و المعادن الظهران – المملكة العربية السعودية نوفمبر ١٩٩٤م

## Chapter 1

## Introduction

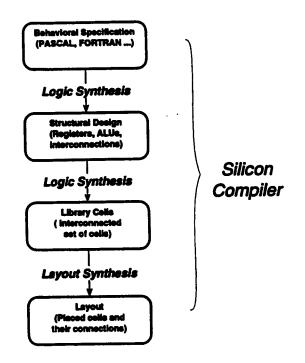

Design automation is the automatic synthesis of a physical design from some higher-level behavioral specification. There are three levels of synthesis namely: high-level synthesis, logic synthesis and layout synthesis. Logic synthesis converts a structural design, in terms of an interconnected set of register transfer level components, into combinational logic, and maps that logic onto cells from a library of a particular technology. Layout synthesis converts an interconnected set of cells, which describes the design structures, into the physical geometry (layout) of the design. An integrated system that contain all three synthesis levels is called *silicon compiler* (see Figure 1.1).

In this work, various intermediate forms from known high-level synthesis systems are surveyed. A classification framework that classifies intermediate forms into two main classes (primary and secondary) is introduced. Essential and desir-

Figure 1.1: Synthesis levels and silicon compiler.

able features of primary intermediate forms are identified. Finally, a new primary intermediate form called Generic Control-Data Flow Graph (GCDFG) is introduced. This GCDFG has all the desirable features of primary intermediate forms and facilitates synthesis tasks like scheduling and allocation. This GCDFG is stored in ASCII, lisp-like format which makes it portable, machine processible, flexible and rich format.

٠:.

This work is divided into five chapters. In chapter one, high-level synthesis is defined and basic terminology like: DFG, CFG, CDFG, transformation, scheduling, allocation etc., are explained. In the second chapter, some known high-level synthesis systems that use various intermediate forms are surveyed. Following the survey, a general classification framework, that classify intermediate forms into two classes: primary and secondary, is introduced. The essential and desirable features that should be possessed by a primary intermediate form are identified. Finally, a new intermediate form that is called the GCDFG is introduced. Based on this new intermediate form, an attributed format called GCD-List is introduced.

In this introductory chapter, abstraction levels and high level synthesis are defined. Following that, basic terminology like: data flow graph (DFG), control flow graph (CFG) and control-data flow graph (CDFG) are introduced and illustrated by examples. Finally, the main tasks of high-level synthesis are defined and explained briefly.

## 1.1 Definition of High-level Synthesis

Digital systems are represented at three abstraction levels: the behavioral level, the structural level and the physical level. The highest level of abstraction which is the behavioral level, corresponds to the high-level description of the system. Behavior means the way the system or its components interact with their environment [4]. At this level the system can be described in a high-level language like: FORTRAN [27], PASCAL[29], C... etc. The next lower level of abstraction is the structural level. At this level the system is described by its hardware components (registers, ALUs ...etc.,) and their interconnection (netlist). This level is also called the Register Transfer Level (RTL). Finally comes the lowest abstraction level which is called the physical level. At this level the digital system is interpreted by the chip layout [6].

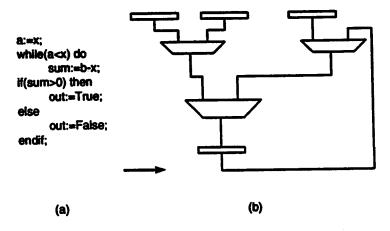

Figure 1.2: Digital system representation. (a) Behavioral level. (b) Structural level.

In general terms, high-level synthesis (HLS) can be defined as the automatic

translation of a high-level description (behavioral level) to a lower abstraction level (structural level). This translation is usually subject to specific constraints like (speed, cost, space ... etc.,) [5, 17, 10, 2](see Figure 1.2).

High-Level Synthesis (HLS) is a very complex process therefore, it is divided into tasks. The high-level description is first transformed into an internal representation (intermediate form (IF)). Next, operations are scheduled into control steps. Then, hardware resources like ALUs, registers ...etc., are allocated to execute these operations in the required control steps. Finally, a controller is synthesized to generate the control signals needed to invoke the allocated hardware components (see Figure 1.2). To perform the aforementioned tasks some intermediate forms are used to help the synthesis process. The most widely used intermediate forms are flow graphs like: data flow graphs (DFG), control flow graphs (CFG)... etc. DFG, CFG and CDFG intermediate forms are explained in detail below.

### 1.1.1 Date Flow Graph (DFG)

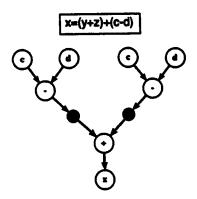

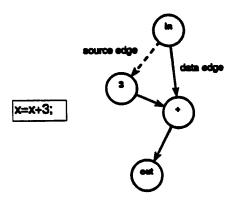

Data Flow Graphs are used to express the data flow of straight codes or basic blocks only. It can be defined as a sequence of statements that has one entry point and one exit point with no iterative, conditional or unconditional jumps. A Data Flow Graph consists of nodes and directed edges. Nodes represent operations as well as operands. The directed edges connect operand nodes to operation nodes or vice versa. A directed edge connecting a variable node to an operation node means this

operand is used as source and each incoming edge means this operand is used as a destination for that operation.

Mathematical and logical operations are either unary or binary. Unary operation nodes have one incoming edge. Binary operation nodes have two incoming edges (the two operands). If more than one operation are performed in the same instruction, some intermediate results have to be stored. These intermediate results are stored in intermediate variable nodes which are represented by small black dots (see Figure 1.3). In non-commutative binary operations like divide and subtract, a convention should be followed. For example (c-d) in Figure 1.3, the first variable c is represented by an incoming edge from the left and the second variable d is represented by an incoming edge form the right.

Figure 1.3: Data flow graph.

### 1.1.2 Control Flow Graph (CFG)

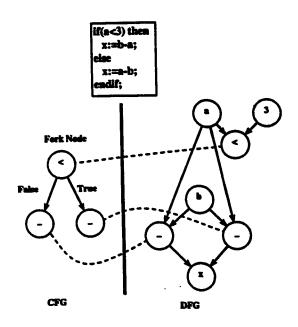

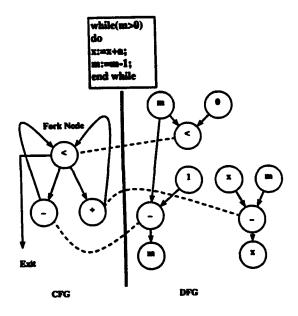

A Control Flow Graph (CFG) is a directed graph, where nodes correspond to operations and edges represent predecessor/successor relationships. There is one to one correspondence between the DFG operation nodes and the CFG nodes. An outgoing edge from node A to node B indicates that operation A is executed before operation B because node B is data dependent on node A (a destination variable in operation A is used as a source variable in operation B). The CFG is used to express conditional and iterative constructs. For Example, to implement an *if-then-else* statement, a fork node is used. The fork node, which carries the *if* condition, has two labeled outgoing edges, one for the true branch and one for the false branch. The condition of the *if* statement is implemented in the DFG. Then based on the condition value the corresponding branch is chosen (see Figure 1.4). Loops are implemented by feedback edges as in Figure 1.5.

## 1.1.3 Control-Data Flow Graph (CDFG)

A high-level synthesis system called ESPRIT [28] translates the high-level language into a Control-Data Flow Graph (CDFG) called extended DFG in which data and control flow graphs are combined. This extended DFG consists of nodes and directed edges. There are three main types of nodes: operation, operand and control nodes. Edges represent predecessor/successor relationships. Example of control edges are

Figure 1.4: The CFG and the DFG representing an if-then-else statement.

Figure 1.5: The CFG and the DFG representing a while loop.

feedback edges.

٠.:.

The CDFG nodes represent operations in the behavioral specification, and the edges model the transfer of values between operations. A single data value instance is defined to be a token. An operation is executed when a token passes from the incoming edge and exits via the outgoing edge. Thus, operations can be executed concurrently without violating data dependencies. Several node types are defined in this CDFG. These types of nodes allow the CDFG to support various high-level constructs. The node types are:

- Operation nodes. These carry mathematical operations symbols like: \*, -, +, /

or boolean like and, or.

- 2. Input/Output nodes. Every graph requires at least one node of type input and one of type output. Nodes of type input have no incoming edges and nodes of type output have no outgoing edge as in Figure 1.6. Input/Output nodes represent source variables and destination variables.

- 3. Constant nodes. These produce constant data values at their outgoing edge.

These nodes have an incoming dashed edge to indicate the timing at which the constant should be generated.

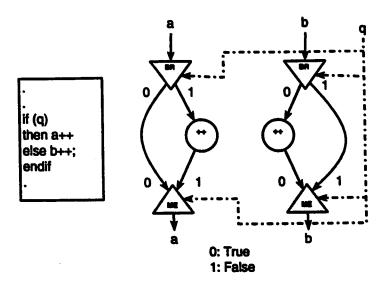

- 4. Branch and Merge nodes. These are used in realizing conditional constructs like if-then-else statement. A branch node passes the token from the incoming edge to one output port, which is selected by the value of the token

Figure 1.6: IN, OUT and constant nodes.

on the control input. In other words, the control input carries one value either 0 or 1, based on that the corresponding branch is selected. For example, in Figure 1.7 when q = 1, the left BR node passes the token to the increment node where a is incremented. When q = 0, the right BR node passes the token to the increment branch and b is incremented.

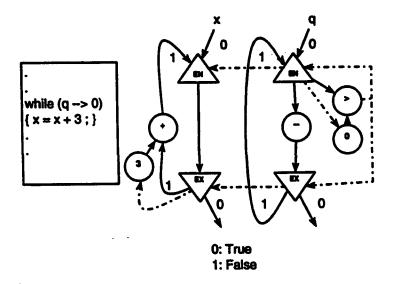

- 5. Exit and Entry nodes are similar to branch and merge nodes, however, they are used to build loop constructs. The loop body and the loop testing condition cause cycles in the CDFG. Using exit and entry nodes makes the identification of the cycles and hence the loop body and the loop condition easier (see Figure 1.8).

- 6. Get and Put nodes provide a mechanism for communication protocols with the outside world. These nodes are linked in a sequential chain to set the order in which read and write operations should appear on the port. These nodes

Figure 1.7: If-then-else construct.

Figure 1.8: While loop with Entry and Exit nodes.

can for instance model pads on the chip boundary (see Figure 1.9).

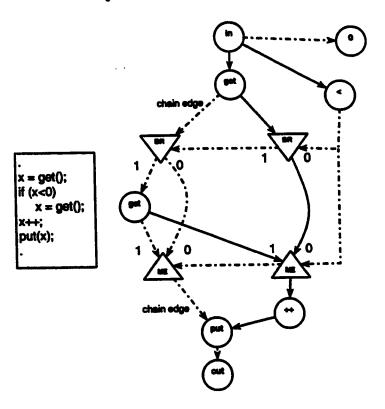

Figure 1.9: Example of Get and Put nodes.

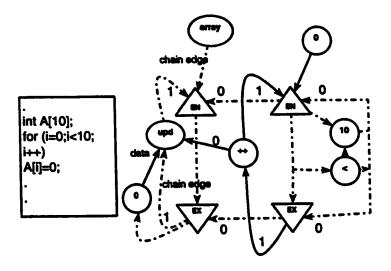

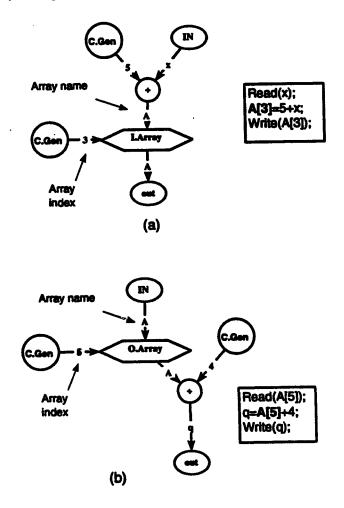

7. Array nodes are used to manipulate array data values. There are basically three types of nodes: Array type is used for declaring the array size and initial values. It has outgoing chained edges which connect it to the other two types namely: retrieve and update. The retrieve type node is used to read data from the array. The update type node is used to write values to the array and it has a data input port that carries the value to be written (Figure 1.10). Chain edges specify the ordering in which the retrieve and update operations should

take place.

Figure 1.10: Array example.

## 1.2 The Main Tasks in HLS

High-level Synthesis (HLS) involves four main tasks namely:

- 1. Transformation or compilation of input specifications.

- 2. Scheduling.

- 3. Allocation and module binding.

- 4. Synthesis of control path and the merging of the control and data paths.

#### 1.2.1 Transformation

This is the first step in HLS. It consists of parsing the high-level input description like behavioral VHDL [25], FORTRAN etc., and transforming it into an internal representation (intermediate form) such as DFG and CFG, CDFG, Value Trace etc.

There are two main approaches in high-level language transformation:

- Two graphs are generated: one for Data (DFG) and one for Control (CFG).

- A Combined Control and Data Flow Graph (CDFG).

#### 1.2.2 Scheduling

Scheduling means assigning operations to control steps so as to minimize a given objective function while meeting constraints. These constraints are usually speed and cost. For example, operations are assigned to control steps so as to maximize hardware resources sharing. Examples of some known scheduling approaches are listed below:

- Exhaustive search. In this method, all scheduling possibilities are tested and the best solution is found. This method finds the optimum solution, however, it has a very high complexity. It can be improved using some branch and bound techniques.

- As Soon As Possible (ASAP). Operations are assigned to their corresponding earliest possible control steps [22].

As Late As Possible (ALAP). Operations are assigned to the latest possible control step [22].

٠..

- List Scheduling. The critical path is scheduled first. Operations to be scheduled in the next control step are ordered in a list based on some priority function like path length and urgency [20].

- Dynamic List Scheduling. DLS is oriented to control-flow dominated designs.

It is a modified version of the known path-based scheduling approach [3]. The algorithm takes VHDL as input and produces a Finite State Machine (FSM) as output. Each transition in this FSM corresponds to a control step [9].

- Freedom-based scheduling. Operations on the critical path are scheduled first,

then operations that have less freedom, and so on.

- Force Directed. In force-directed scheduling, a global time constraint is specified and the algorithm tries to minimize the resources required to meet that time constraint. By scheduling similar operations in different control steps, it is ensured that the functional units have high utilization and hence, concurrency is balanced [22, 23].

## 1.2.3 Allocation and Module Binding

Allocations means assigning operations, variables and interconnection to different hardware resources like registers, ALUs, multiplexers etc., while meeting constraints

to match a specific objective function such as minimizing total interconnection length, minimizing total hardware cost, minimizing critical path delays, minimizing design area and maximizing total throughput.

Some of the reported allocation algorithms are:

- Clique partitioning. This method consists first of constructing a conflict graph, then using node coloring or clique partitioning techniques to allocate the minimum possible number of resources [31].

- 2. Cost function allocation. In this method each ALU is assigned a cost. After each allocation a cost formula is used to evaluate the cost of the overall ALU allocation. This process is repeated until a satisfactorily low cost allocation is reached. Allocation is conducted so as to minimize the overall cost [21].

# 1.2.4 Control Path Synthesis and Merging Data and Control Path

Scheduling and allocation produce a data-path and a finite state machine (FSM).

In the FSM, the states correspond to control steps and the edges correspond to the conditions that cause transition from a state to another. From the FSM and the data path, the controller is synthesized. This controller is then interfaced with the data path to generate the signals that drive the data-path resources.

## Chapter 2

## Intermediate Forms and

# **High-Level Synthesis Tasks**

This chapter discusses the synthesis tasks and the intermediate forms used in these tasks in several high-hevel hynthesis systems. Different high level synthesis systems have been chosen to illustrate the various types of intermediate forms that are in use. It consists of three main sections. The first section surveys intermediate forms used in transformation. The second section discusses intermediate forms used in scheduling and the third section discusses intermediate forms used in allocation.

## 2.1 Intermediate Forms Used in Transformation

In this section, high-level languages and the intermediate forms used with them are surveyed. In high-level synthesis, the target design [12, 11] can be specified using:

- a hardware description language like behavioral VHDL [26];

- 2. a high-level language: C, FORTRAN [27], PASCAL [29]... etc.

The aforementioned categories of languages share common characteristics. They describe data manipulation in terms of assignments of variables that keep their values until they are overwritten. Statements are sequentially organized in blocks linked by control transfer constructs like conditional constructs, and looping. Hierarchy is achieved by dividing large programs into subprograms (subroutines and procedures).

The study conducted here includes procedural languages only. However, there have been some experiments with nonprocedural specification languages, such as applicative (LISP) and declarative or rule based languages such as PROLOG [7]. In what follows, some HLS systems, their high-level languages and the supporting intermediate forms are surveyed. Three high-level synthesis systems are discussed. They are: HARP, Classical, and HAL. As will be seen later, these three are chosen because they use different approaches.

#### 2.1.1 Transformation in HARP

The Hardware Architecture Ruling Processor (HARP) synthesis system uses a subset of the ANSI FORTRAN 77 [27] as a behavioral specification language. The FORTRAN code is translated into a DFG. Since DFG can only express basic blocks, the following assumptions and restrictions are observed:

- 1. Subroutines and functions can be used in the high-level description, however, they are flattened in the DFG.

- 2. Loops with indefinite iterations are not allowed and loops with finite length are enrolled.

- 3. Intrinsic (built-in) functions are not supported.

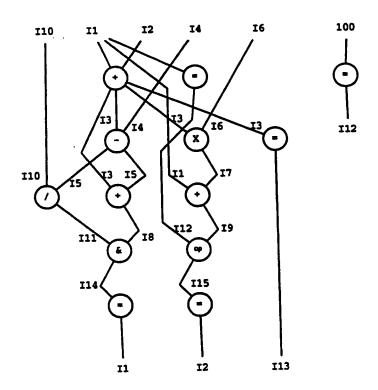

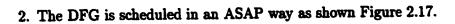

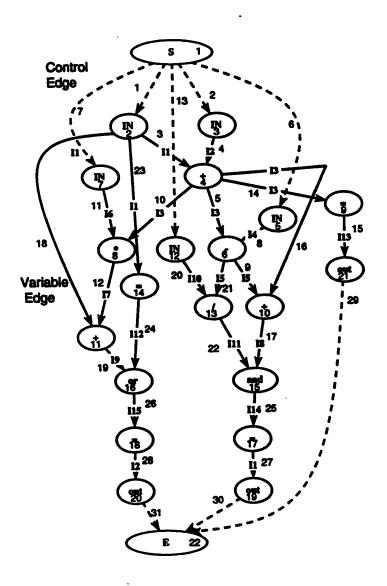

Before the FORTRAN code is translated into a DFG all procedures have to be expanded in-line and loops have to be unrolled. The FORTRAN code of Figure 2.1 is translated into a DFG in which nodes represent operations as well as operands and edges represent input/output relationships (see Figure 2.2).

DFG exposes the maximum potential parallelism of a high-level specification. For example, the basic block of Figure 2.1 can be realized by the DFG of Figure 2.2. From this DFG an equivalent parallel basic block can be written as in Figure 2.3. Instructions that are written in the same line are data independent and hence can be executed in parallel. Transforming a straight piece of code into a DFG is a

```

DATA I1,I2,I3,I4,I5,I6.I7,I8,I9,

& I10,I11,I12,I13,I14,I15

/ 1,2,3,4,5,6,7,8,9,

8 10,11,12,13,14,15 /

I3 = I1 + I2

I5 = I3 - I4

I7 = I3 * I6

I8 = I3 + I5

I9 = I1 + I7

I11 = I10 / I5

I12 = 100

I13 = I3

I12 = I1

I14 = IAND(I11,I8)

I15 = IOR(I12,I9)

I1 = I14

I2 = I15

STOP

END

```

Figure 2.1: High-level specification (basic block).

·:.

Figure 2.2: The corresponding DFG of the FORTRAN code of Figure 2.1.

```

I3 = I1 + I2; I12 = I1; I12 = 100; I5 = I3 - I4; I2 = I3 * I6; I13 = I3; I8 = I3 + I5; I11 = I10 / I5; I9 = I1 + I7; I14 = IAND(I11,I8); I15 = IOR(I12,I9); I1 = I14; I2 = I15;

```

Figure 2.3: Parallel code reconstructed from the DFG of Figure 2.2. reversible process. In other words, an equivalent description of the original code can be recovered from the DFG.

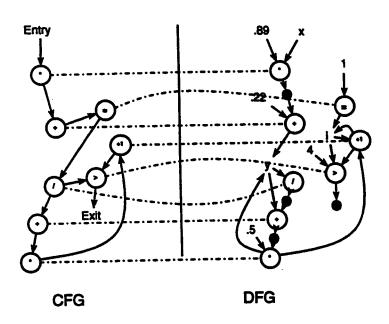

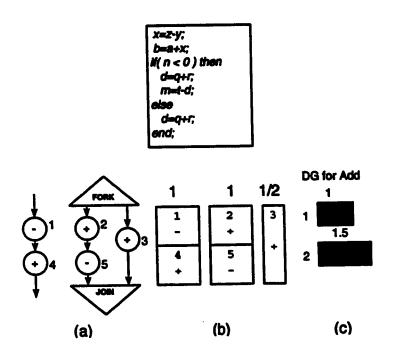

## 2.1.2 Transformation in the Classical System

The classical system is a generic HLS system introduced in [32] by Camposano, where synthesis starts from a behavioral VHDL description. A DFG and a CFG are built, then scheduling and allocation are performed. The data-path is constructed from the DFG and the corresponding control path is constructed with the help of a FSM. Finally, the data-path and the control-path are merged together to form the RTL design of the input specification.

Behavioral VHDL can be represented graphically by an intermediate form called DAG (Directed Acyclic Graph). The graph nodes represent procedures and edges represent the calling relationships. Nodes and edges have attributes, examples of node attributes are procedure name, type of hardware (combinational or sequential).

Each VHDL procedure is transformed into a Data Flow Graph (DFG) and a

Control Flow Graph (CFG). DFG is a graph where nodes represent operations as well as operands and edges represent input/output relationships as in Figure 2.4.

The small filled nodes in the DFG are those variables that do not exist in the high-

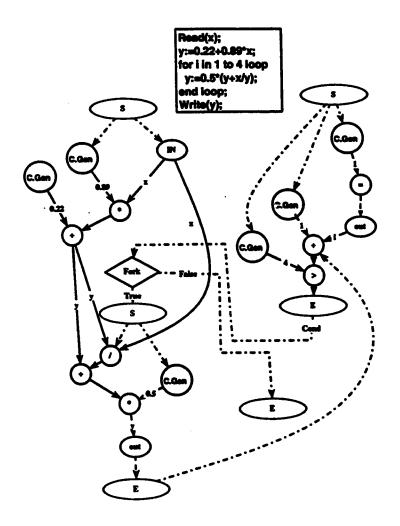

y:=0.22+0.89+x; for i in 1 to 4 loop y:=0.5\*(y+x/y); end loop;

Figure 2.4: The corresponding DFG of the FORTRAN code of Figure 2.1.

level code. Operation nodes have operation type as attributes and variable nodes have type of variable as attribute. CFG is a directed graph where nodes represent operations and edges represent predecessor/successor relationship (Figure 2.4).

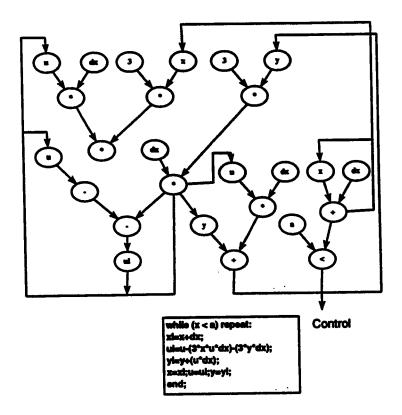

#### 2.1.3 Transformation in HAL

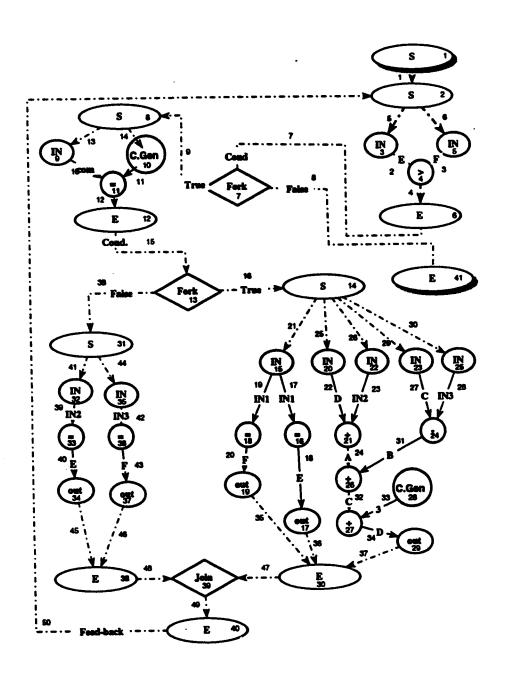

In HAL [22] synthesis starts from a high-level language (HLL). The high-level language HLL which has a PASCAL like syntax and semantics is translated into a combined Control Data Flow Graph (CDFG) (see Figure 2.5). In the CDFG, nodes represent operations, constants, and variables. Edges represent input/output relationships and data dependency. Moreover, dummy timing nodes can be inserted between two nodes (operation); these are used to enforce a given execution order of the corresponding operations like forcing a specific operation to be executed before or concurrently with another operation. Conditional constructs like: *if-then-else* and *case* can be represented in the CDFG by attaching the *condition* to the edge. These require fork and join nodes as we will see later.

## 2.1.4 Summary

The results of the above study are summarized in Tables 2.1 and 2.2. Table 2.1 shows the high-level languages versus the features they support. In the Classical system the input description is VHDL which supports all the necessary high-level language features. In HAL synthesis system a generic PASCAL like language is used. The HLL in HAL supports all the necessary high-level language features except hierarchy where it is not clear from the literature whether it is supported or not. In HARP FORTRAN 77 is used as an input description language. All necessary high-level

Figure 2.5: Combined Control and Data Flow Graph.

language features are supported in the FORTRAN 77 except concurrency. Finally, In ESPRIT a generic C-like language is used. All necessary high-level language features are supported except hierarchy and concurrency.

| System      | Classical | HAL | HARP    | ESPRIT |

|-------------|-----------|-----|---------|--------|

| Language    | VHDL      | HLL | FORTRAN | HLL    |

| Sequencing  | Yes       | Yes | Yes     | Yes    |

| Hierarchy   | Yes       | -   | Yes     | •      |

| Conditional | Yes       | Yes | Yes     | Yes    |

| Looping     | Yes       | Yes | Yes     | Yes    |

| Concurrency | Yes       | No  | No      | -      |

Table 2.1: High-level languages and their supporting features.

In Table 2.2, we summarize the features supported by each intermediate form. As seen clearly sequencing and concurrency of operations are supported by all types of flow graphs. Conditional constructs and looping are supported by DFG+CFG, CDFG and the extended DFG. Hence, DFG representation alone is not enough to realize conditional constructs and looping. It was not stated in most of the literature whether hierarchy is supported or not. However, in HARP it has been clearly stated that hierarchy is not supported and all subroutines should be in-line expanded before translation.

| System            | Classical | HAL  | HARP | ESPRIT       |

|-------------------|-----------|------|------|--------------|

| Intermediate Form | DFG+CFG   | CDFG | DFG  | Extended DFG |

| Sequencing        | Yes       | Yes  | Yes  | Yes          |

| Hierarchy         | -         | -    | No   |              |

| Conditional       | Yes       | Yes  | No   | Yes          |

| Looping           | Yes       | Yes  | No   | Yes          |

| Concurrency       | Yes       | Yes  | Yes  | Yes          |

٠.: .

Table 2.2: Intermediate forms and their supporting constructs.

# 2.2 Intermediate Forms Used in Scheduling

In this section, some scheduling techniques and their intermediate forms used in some high-level synthesis systems are discussed. The scheduling techniques that will be explained are as soon as possible (ASAP), path-based [3] and force-directed scheduling [22]. Scheduling means assigning operations to control steps so as to minimize a given objective function while meeting constraints. These constrains are usually speed and cost. Examples of speed constraints are number of control steps and length of the control step. Examples of cost constraints are number of functional units, registers, interconnections, buses and multiplexers.

There are two basic types of scheduling algorithms:

Transformational. These are the ones that begin with a default schedule

(maximally parallel or serial). Then several transformations are applied to get

the final schedule. Examples of transformational scheduling algorithms are:

the exhaustive search and the ad-hoc heuristics such as the one used in HARP

[27].

• Iterative/Constructive. This type adds operations one at a time until all operations are scheduled. For example: ASAP, ALAP and force-directed.

## 2.2.1 ASAP and ALAP Scheduling

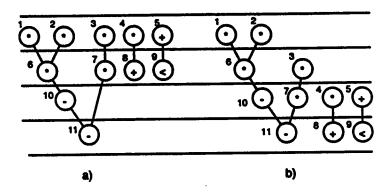

In ASAP scheduling, operations are assigned to the earliest possible control step as shown in Figure 2.6(a). In As Late As Possible (ALAP), operations are assigned to the latest possible control step (see Figure 2.6(b)).

Figure 2.6: (a) ASAP scheduling. (b) ALAP scheduling.

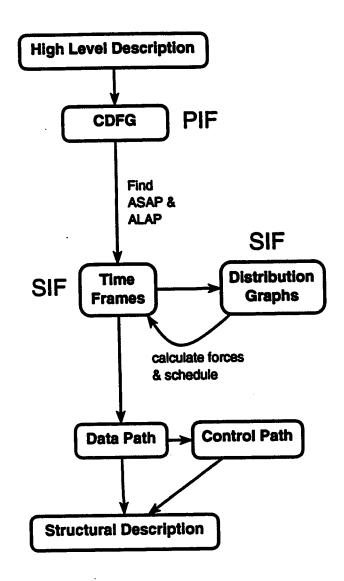

## 2.2.2 Force-Directed Scheduling in HAL

In HAL synthesis system a scheduling technique called force-directed is used. In force-directed scheduling [23], a global time constraint is specified and the algorithm tries to minimize the hardware resources required to meet that time constraint. By

placing similar operations in different control steps, it is ensured that the functional unit has high utilization and the concurrency is balanced. The force-directed scheduling proceeds as follows:

### 1. Determine Time Frame:

A time frame corresponds to an operation in the CDFG. The length of the time frame is calculated by evaluating the ASAP and the ALAP schedules as in Figure 2.6. The difference between the two schedules is equal to the length of the time frame (see Figure 2.7). The width of a time frame is equal to 1/length. Hence the area of each time frame is always one. The time frame width indicates the probability of scheduling the corresponding operation in the control step(s) covered by the time frame. For example, in Figure 2.7 the ASAP schedule of the "<" operation is in step 2 and its ALAP is in control step 4. So the time frame of the operation "<" spans three control steps (control step 2 to control step 4) and its width is  $\frac{1}{3}$ . The time frame of operation "<" has a length of 3 and a width of  $\frac{1}{3}$ , and hence, its area is equal to:  $3*\frac{1}{3}=1$ .

## 2. Create Distribution Graph (DG):

Operation types are separated into disjoint sets. For each set the time frames are added to form a Distribution Graph. In this example there are four types of operations, namely: multiply, add, subtract and compare. They are separated

Figure 2.7: Time frames and distribution graph. (a) For multiply operation. (b) For add, subtract and compare operations.

into two disjoint sets: { multiply } and { add, subtract, compare }. For example the DG of the first set of operations { multiply } in control step 2 is equal to the summation of the time frames of multiply operations in step 2 and in this case they are operations number: 4, 6 and 7. Which makes the DG for step  $2 = 1 + \frac{1}{2} + \frac{1}{3} = 1.8$  (see Figure 2.7).

3. Calculate the force associated with each control step assignment for each operation as follows:

$$F(op) = \sum_{j=1}^{N} (DG(j)) * x(op, j)$$

$j = control \ step$

$op = operation$

$x(op, j): \ change \ of \ probability \ of \ scheduling \ operation \ op \ in \ control \ step \ j$

For example, to schedule the multiply (operation 3) in step 1 then, the probability of this operation will change from  $\frac{1}{2}$  to 1 in step 1 and from  $\frac{1}{2}$  to 0 in step 2. This will result in a force equal to:

$$F(*_3) = (DG(1) * x(3,1)) + (DG(2) * x(3,2))$$

$$= (2.833 * 0.5) + (2.333 * (-0.5))$$

$$= 0.25$$

The force is positive, because control step 1 is congested, hence scheduling operation 3 in control step 1 will have an adverse effect on the overall balance.

- 4. Choose the force with the largest negative value and schedule the corresponding set of operation(s) in the corresponding control step.

- 5. Update time frames and distribution graph as in Figure 2.8 and repeat from step (1) until all operations are scheduled.

Figure 2.8: Final time frames and distribution graph.

#### **Scheduling Conditional Branches**

٠.,

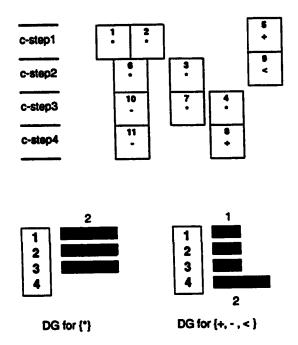

Conditional Constructs such as if-then-else statements cause forks in the CDFG as shown in Figure 2.9. Operations in different branches of a fork are mutually exclusive. When operations in different branches can be executed on the same type of FU, they can be scheduled into the same control-step without increasing the required number of FUs. Therefore, the same FU will be shared by those operations since they will never execute concurrently. To take advantage of this observation, the following is performed. For each control-step in which the time frames of the mutually exclusive operations intersect, only the highest probability of these is added to the corresponding DG. For example, for the "+" operation in Figure 2.9, which has a time frame spanning two control steps (steps 1 and 2), the distribution graph is made equal to 1 rather than  $1+\frac{1}{2}=1.5$ . This is illustrated in Figure 2.9. Without special treatment of the mutually exclusive additions, the total distribution would be 1.5 in both control-steps. The unscheduled addition would then have an equal probability of being assigned to either control-step. It is obviously preferable to schedule it in the first control-step, since in this case only one adder will be required. This is due to the reduced distribution in the first control-step.

Figure 2.9: Behavioral description with an *if* statement and the corresponding: (a) CDFG. (b) Time frames. (c) DG.

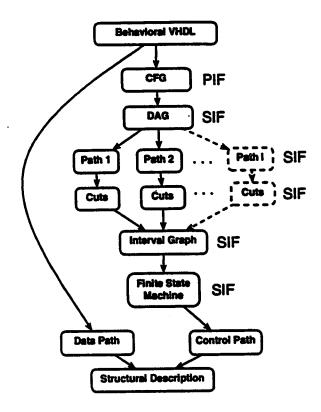

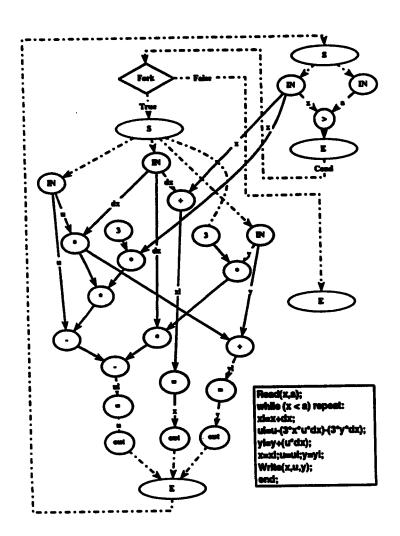

### 2.2.3 Path-Based Scheduling

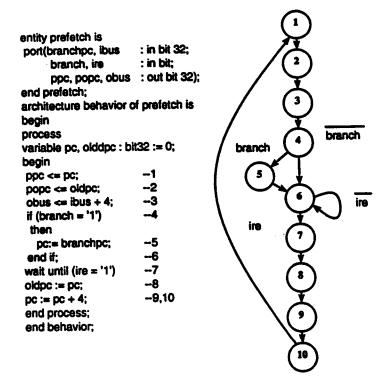

Path based scheduling [3] minimizes the number of control steps under given constraints. Conditional branches and conditional constructs are taken care of in path-based scheduling technique. Scheduling is applied on a CFG where nodes represent operations and edges represent precedence relationship. Edges have attributes (the condition of if and while statements), as illustrated in Figure 2.10.

Figure 2.10: Behavioral description of an instruction fetch unit for a micro-processor, and the corresponding CFG.

The algorithm is applied in four steps:

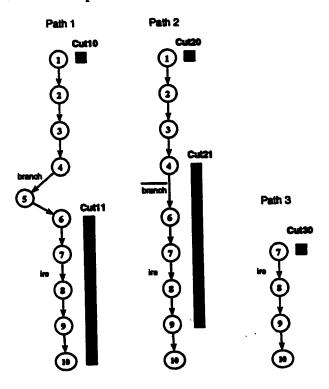

1. The CFG of Figure 2.10 is transformed into a directed acyclic graph (DAG).

This is done by removing the feedback edges from the CFG.

- 2. All possible paths in the DAG are identified and scheduled independently in ASAP manner. A path represents a possible sequence of operations.

- 3. For each path all constraints are computed. Constraints are as follows:

- (a) Variables can be assigned only once in a control step.

- (b) I/O ports can be read or written only once in a control step.

- (c) FUs can be used only once in a control step.

- (d) The control step duration limits the number of operations that can be chained in that control step.

Each constraint can be interpreted as an interval that covers a set of operations, hence a constraint can be interpreted as a set of operations. For instance, the variable pc is written twice between operations 5 and 10, so constraint (a) indicates that path 1 has to be cut between operations 6 and 10, this is illustrated in Figure 2.11.

An interval graph is formed for each set of constraints. In the interval graph, each node represents an interval and an edge indicates that the two intervals overlap as in Figure 2.11. The number of cliques in a minimum clique cover corresponds to the minimum number of control steps. Each clique corresponds to a cut. This illustrates which operation will be executed in the corresponding

control step. Beside that, one cut (cut0) is added to the first operation in the CFG (see Figure 2.11). These cuts give the minimum number of control steps needed to execute that path.

Figure 2.11: Constraints and interval graph.

4. Schedules of all paths, which are created in step 2, are overlapped so as to minimize the number of control steps. A graph is formed where the nodes correspond to the cuts generated in step 3 and the edges join nodes corresponding to overlapping cuts as in Figure 2.11. A minimum clique cover of this graph gives the least set of cuts and hence the minimum number of control steps (states) that satisfy the ASAP schedule for all paths.

5. The finite state machine (FSM) with the minimum number of control steps (states) that is calculated from step 4, is built (see Figure 2.12).

Figure 2.12: The control finite state machine.

#### 2.2.4 Summary

A study of several intermediate forms and scheduling techniques has been conducted.

ASAP and ALAP scheduling techniques can be easily applied to DFGs. As shown previously, force-directed scheduling can be applied on CDFG after obtaining the ASAP and the ALAP schedules. Hence, force-directed scheduling can also be applied to CDFGs. Force-directed Scheduling takes care of loops and conditional constructs. Path-based scheduling, operates on CFGs and takes care of loops and conditional constructs. The aforementioned results are summarized in Table 2.3.

|                | CDFG | DFG | CFG |

|----------------|------|-----|-----|

| ASAP and ALAP  | Yes  | Yes | Yes |

| Force-directed | Yes  | Yes | No  |

| Path-based     | Yes  | Yes | Yes |

٠:.

Table 2.3: Intermediate forms and scheduling techniques.

# 2.3 Intermediate Forms Used During Allocation

In this section various intermediate forms that are used during allocation are surveyed. Allocations can be defined as assigning operations, variables and communication paths to different hardware resources like: ALUs, registers, buses, multiplexers... etc., while meeting constraints like: total interconnections length, total hardware cost, critical path delays and design area [30]. In what follows, we describe how allocation is performed in various HLS systems together with the intermediate forms used for this task.

# 2.3.1 Allocation in FACET Synthesis System

FACET is a HLS system designed at CMU [31]. It uses a unified allocation procedure. FACET is not surveyed in the previous sections (transformation and scheduling), because the synthesis starts from a scheduled code sequence (straight code) which can be thought of as a scheduled DFG. The objectives are to minimize the number of FUs, storage elements, and interconnection units [31]. The synthesis process starts from a scheduled code sequence (straight code) as in Figure 2.13.

```

Step No.

V12 = V1;

V3 = V1 + V2;

1

V13 = V3

V2 = V3 * V6;

V5 = V3 - V4;

2

V8 = V3 + V5;

V11 = V10 / V5

V9 = V1 + V7;

3

V14 = V11 \text{ and } V8; V15 = V12 OR V9;

4

V2 = V15;

V1 = V14;

```

Figure 2.13: A code sequence.

#### Registers Allocation

The code sequence contains many variables. The purpose here is to combine as many variables as possible in the least possible number of registers. A variable is said to be *live* between the time of its first definition and last use. A variable is said to be *dead* between the time of its last use and its next definition. Table 2.4 shows the variables and their life-times (L=Live and D=Dead). If the live periods of two variables do not overlap then, they have disjoint life-time. Obviously two variables can be combined and hence stored in the same register if they have disjoint life-times. Relaxing this restriction, two variables are combinable if their life-times overlap in a step in which one of them is assigned to the other.

To combine variables in a minimum possible number of registers, a compatible graph is formed. In this compatible graph, nodes correspond to variables. Each two combinable registers are joined by an edge. To form a compatible graph, a complete graph is formed first, then edges that join two variables with overlapping life-times are deleted. The resulting graph is represented in Figure 2.14 where each

```

(2,7)

(2,3)

(2,5)

(1,13)

(1,14)*

(1,9)

(2,15)*

(3,8)

(2,9)

(2,13)

(2,11)

(2,8)

(5,11)

(3,15)

(4,13)

(5,8)

(3,13)

(3,14)

(7,9)

(7,13)

(5,15)

(6,13)

(5,13)

(5,14)

(8,14)

(9,13)

(9,15)

(8,13)

(7,14)

(7,15)

(13,14)

(12,15)

(11,14)

(12,13)

(10,13)

(13, 15)

```

Figure 2.14: The edge list of the compatible variable graph.

pair represents two nodes (variables) connected by an edge. Edges that are tagged with "\*" indicate pure data transfers like (V1 = V14).

| Time | v1  | v2  | v3 | v4   | v5 | v6       | v7                 | v8       | v9 | v10      | v11      | v12                | v13 | v14      | v15 |

|------|-----|-----|----|------|----|----------|--------------------|----------|----|----------|----------|--------------------|-----|----------|-----|

| Etry | L   | L   | D  | L    | D  | L        | D                  | D        | D  | L        | D        | D                  | D   | D        | D   |

| 1    | T.  | T.  | L  | L    | D  | L        | ם ו                | ם        | D  | L        | D        | L                  | D   | D        | D   |

| . 2  | ī.  | ם ו | L  | T.   | L  | L        | L                  | D        | L  | L        | D        | L                  | D   | D        | D   |

| 3    | T   | D   | T  | ī.   | L  | L        | L                  | L        | L  | L        | L        | L                  | D   | D        | D   |

| 1 4  | ן ה | ח   | Ď  | l t. | מו | L        | $\bar{\mathbf{q}}$ | L        | L  | L        | L        | L                  | D   | L        | L   |

| 1 4  | -   | 1   | n  | ī    | D  | l T      | n                  | <u>_</u> | D  | L        | ם        | ם                  | Q   | L        | L   |

| 5    | -   | ‡   | 12 | -    | 2  | -        | 7                  | 2        | ח  | T        | מ        | $\bar{\mathbf{p}}$ | מ   | ם  <br>מ | D   |

| Exit | L   | l L | ען | L    | ען | <u> </u> | ע                  | ע        | עו | <u> </u> | <u> </u> | <u> </u>           |     |          |     |

Table 2.4: Life-time table.

The compaction procedure works as follows. First, variables that are related by pure data transfers are combined. This is done by merging the nodes corresponding to these variables. This might lead to a reduction in the number of control steps. For example step 5 is cancelled because it contains two instructions which are pure data transfers (V1 = V14, V2 = V15). After that, the clique partitioning algorithm is applied on the graph of Figure 2.14. The algorithm partitions the set of vari-

ables into a minimum number of disjoint subsets. The resulting subsets (cliques) are {1,14}, {2,7,9,15}, {3,8,13}, {4}, {5,11}, {6}, {10} and {12}. The variables in each of these subsets can be assigned to one physical register, as follows:

Register 1 holds variables V1 and V14.

Register 2 holds variables V2, V7, V9 and V15.

Register 3 holds variables V3, V8 and V13.

Register 4 holds variable V4.

Register 5 holds variables V5 and V11.

Register 6 holds variable V6.

Register 7 holds variable V10.

Register 8 holds variable V12.

Therefore, only eight registers are needed to store these fifteen variables.

#### **Functional Unit Allocation**

To allocate the minimum number of FUs, similarities between the code sequence instructions are identified. For example, if two instructions have the same operation and the same operands but different destinations, then the FU and the connections from the source registers can be shared between these two instructions. Only a decoder has to be inserted at the FU output to select the desired destination. By looking at the input code sequence of Figure 2.13 it is clearly seen that the relation

#### between any two instructions has to be one of the following:

- The operations and all three variables (destination and two sources) are different.

- 2. The operations are the same. All three pairs of variables are different.

- One pair of the variables is the same. The operations and the other two pairs of variables are different.

- 4. The operations and one pair of variables are the same. The other two pairs of variables are different.

- 5. Two pairs of the variables are the same. The operations and one pair of variables are different.

- 6. The operations and two pairs of variables are the same. The third pair of variables is different.

- 7. The operations are different but the three pairs of variables are the same.

- 8. The operations and the three pairs of variables are all the same.

First a complete graph, whose nodes represent FUs, is constructed. Edges that connect simultaneously used FUs (nodes) are deleted to form the compatible graph. Then clique partitioning is applied on Figure 2.15. Hence, all operations are combined in three FUs as follows:

Figure 2.15: The edge list of the FUs compatible graph.

- 1. FU1 implements "+" in step 1, "\*" in step 2, "+" in step 3, and "or" in step 4.

- 2. FU2 implements "-" in step 2, "+" in step 3, and "and" in step 4.

- 3. FU3 implements "/" in step 3.

#### **Interconnections Allocation**

Interconnections that are never used simultaneously can be grouped into one bus.

The interconnections problem consists of grouping all the interconnections into the minimum number of busses. This problem is very similar to the registers and the FUs allocation problem and it is solved in the same manner. A complete graph is formed where nodes represent interconnections between hardware resources (registers and FUs) (Table 2.5). Edges that connect simultaneously used interconnections are deleted. The clique partitioning algorithm is applied on the compatible graph of Figure 2.16 and the interconnections are combined into eight buses. All the 17

| Source   | Destination | Indexing |

|----------|-------------|----------|

| Name     | Name        | Integer  |

| V1       | V12         | 1        |

| V1       | ALU1.In1    | 2        |

| V2       | ALU1.In2    | 3        |

| V3       | ALU1.In1    | 4        |

| V3       | ALU2.In1    | 5        |

| V4       | ALU2.In2    | 6        |

| V5       | ALU2.In2    | 7        |

| V5       | ALU3.In2    | 8        |

| V6       | ALU1.In2    | 9        |

| V10      | ALU3.In1    | 10       |

| V12      | ALU1.In1    | 11       |

| ALU1.Out | V2          | 12       |

| ALU1.Out | V3          | 13       |

| ALU2.Out | V1          | 14       |

| ALU2.Out | V3          | 15       |

| ALU2.Out | V5          | 16       |

| ALU3.Out | V10         | 17       |

Table 2.5: Indices of interconnections.

Figure 2.16: The edge list of the interconnections compatible graph.

interconnections of Table 2.5 are combined into 8 buses as follows:

Bus No. 1 replaces interconnections {13,14,15,16}.

Bus No. 2 replaces interconnections {1,2,4,11}.

Bus No. 3 replaces interconnections {6,7,8}.

Bus No. 4 replaces interconnections {3,9}.

Bus No. 5 replaces interconnections {5}.

Bus No. 6 replaces interconnections {10}.

Bus No. 7 replaces interconnections {12}.

Bus No. 8 replaces interconnections {17}.

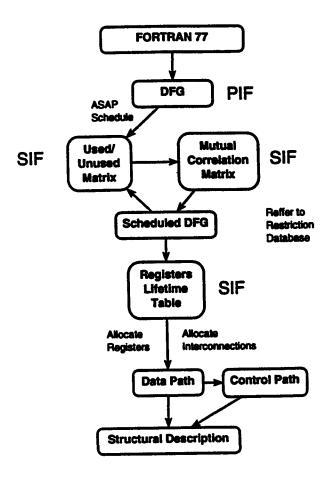

## 2.3.2 Allocation in HARP

In HARP allocation is conducted in three phases: ALUs allocation, then registers allocation, and finally, interconnections allocation. straight

#### **ALU Allocation**

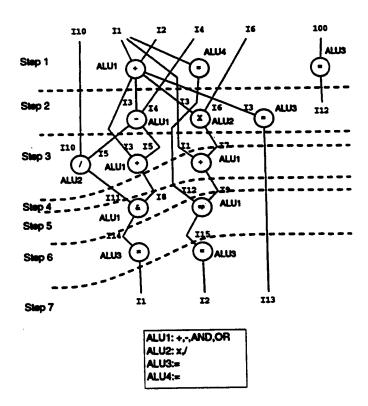

The High-Level Description in HARP is a basic block (straight code) written in FORTRAN 77 (see Figure 2.1). Scheduling and ALUs allocation are iterated in HARP and they are conducted as follows:

1. The FORTRAN code of Figure 2.1 is translated into a DFG as in Figure 2.2.

Figure 2.17: Initial schedule for the FORTRAN code of Figure 2.1.

- 3. Initial allocation is conducted by allocating one ALU for every operation.

- 4. A used/unused matrix is constructed in which each column represents an ALU and each row represents a control step. If a specific ALU is used in a control step then 1 is filled in the corresponding column/row location otherwise 0 is filled, (see Table 2.6). The used/unused matrix is constructed as follows:

$$U_{ns} = \begin{cases} 1, & \text{if ALU } n \text{ is used at step } s \\ 0, & \text{otherwise} \end{cases}$$

Table 2.6: Used/unused matrix.

5. From the used/unused matrix, a mutual correlation matrix is obtained as in Table 2.8. The mutual correlation matrix elements are computed as follows:

$$M(i,j) = \sum_{s=1}^{STEP} U_{is}.U_{js}$$

where STEP is equal to the number of control steps.

| Group Number | Merge Table Operators |

|--------------|-----------------------|

| 1            | *,/                   |

| 2            | +,-,AND,or,           |

| 3            | =                     |

Table 2.7: Restriction database.

6. The mutual correlation matrix is searched for the minimum number and by referring to a restriction database (Figure 2.7). Mergeable ALUs can be detected and merged. For example, element (2,5) which indicates ALU2(\*,/) and ALU5(=) is found to be the minimum. By referring to the restriction database, it is found that it is not possible to merge {\*,/} and {=}. Next,

element (1,3) is found and ALU3 and ALU1 are mergeable, so they are merged to form ALU1 (see Table 2.8).

| l   |   |   |   | l | Next function unit definition    |

|-----|---|---|---|---|----------------------------------|

| 4   | 2 | 2 | 2 | 1 |                                  |

| 1 2 | 2 | 1 | 1 | 0 | ALU1:{+,-,AND, OR}               |

| 2   | 1 | 2 | 0 | 0 | ALU1:{+,-,AND, OR}<br>ALU2:{*,/} |

| 2   | 1 | 0 | 3 | 2 | ALU4:{=}                         |

| 1   | 0 | 0 | 2 | 2 | ALU5:{=}                         |

Table 2.8: Mutual correlation matrix.

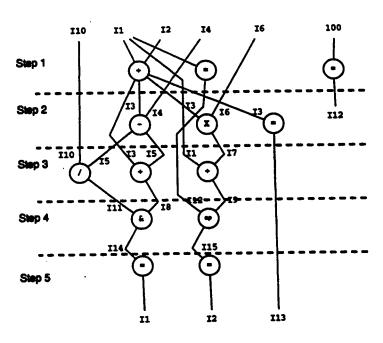

- 7. After each ALU merge, the DFG is re-scheduled according to the new allocation. This leads to an increase in the number of control steps (see Figure 2.18).

- 8. Steps 4 through 7 are repeated until a predetermined maximum number of control steps is reached. In this case this predetermined number is 7 (see Figure 2.18).

#### Registers allocation

A life-time table is constructed. The columns of the life-time table correspond to variables and the rows correspond to control steps. In Table 2.9, "d" corresponds to a variable definition and "r" corresponds to a variable reference. For each variable (column), L (Live) is put in the interval [d,r], D (Dead) is put in the interval [r,d] and U (Unknown) otherwise (see Table 2.10). In Table 2.11 entries that contain

Figure 2.18: Final schedule and the allocated ALUs.

"U" are determined precisely and they are changed to either "l" for Live or "d" for Dead. Variables that do not have overlapping life-times can be allocated to the same register. Example of that is merging I13 with I12, I2 with I7, I5 with I15...etc. The heuristic that combines these registers is the left-edge algorithm which is widely used for channel routing.

| Step  | 12 | 1 | 3 | 2 | 13 | 7 | 6 | 5 | 4 | 11 | 10 | 8 | 9 | 14 | 15 |

|-------|----|---|---|---|----|---|---|---|---|----|----|---|---|----|----|

| entry |    |   |   |   |    |   |   |   |   |    |    |   |   |    |    |

| 1     | d  | r | d | r |    |   |   |   |   |    |    |   |   |    |    |

| 2     |    |   | r |   | d  | d | r | d | r |    |    |   |   |    |    |

| 3     |    |   | r |   |    |   |   | r |   | d  | r  | d |   |    |    |

| 4     |    | r |   |   |    | r |   |   |   |    |    |   | d |    |    |

| 5     |    |   |   |   |    |   |   |   |   | r  |    | r |   | d  |    |

| 6     | r  | d |   |   |    |   |   |   |   |    |    |   | r | r  | d  |

| 7     |    |   |   | d |    |   |   |   |   |    |    |   |   |    | r  |

Table 2.9: Definition and reference history.

| Step          | 12 | 1  | 3  | 2                  | 13       | 7 | 6 | 5 | 4   | 11 | 10 | 8 | 9        | 14 | 15 |

|---------------|----|----|----|--------------------|----------|---|---|---|-----|----|----|---|----------|----|----|

| entry         | D  | L  | D  | L                  | D        | D | L | D | L   | D  | L  | D | D        | D  | D  |

| 1             | L  | L  | L  | L                  | D        | D | L | D | L   | D  | L  | D | D        | D  | D. |

| $\frac{1}{2}$ | L  | L  | L  | D                  | U        | L | L | L | L   | D  | L  | D | D        | D  | D  |

| 3             | L  | L  | L  | D                  | Ū        | L | U | L | U   | L  | L  | L | D        | D  | D  |

| 4             | Ī. | τ. | Ū  | $\bar{\mathbf{Q}}$ | Ū        | L | Ū | Ū | U   | L  | U  | L | L        | D  | D  |

| 5             | L  | D  | Ü  | D                  | Ū        | Ū | Ū | Ŭ | Ū   | L  | Ū  | L | L        | L  | D  |

| 6             | L  | II | U  | D                  | Ŭ        | Ū | Ŭ | Ū | Ū   | Ū  | Ū  | U | L        | L  | L  |

| 7             | IT | TT | II | II                 | U        | U | Ŭ | Ü | · Ü | Ü  | Ū  | Ū | Ū        | Ū  | L  |

| l _ ′         | U  | U  | U  | <u>.</u>           | <u> </u> |   |   |   |     |    |    |   | <u> </u> |    |    |

Table 2.10: Preliminary life-time table.

| Step  | 12 | 1 | 3 | 2 | 13 | 7 | 6 | 5 | 4 | 11 | 10 | 8 | 9 | 14 | 15 |

|-------|----|---|---|---|----|---|---|---|---|----|----|---|---|----|----|

| entry | D  | L | D | L | D  | D | L | D | L | D  | L  | D | D | D  | D  |

| 1     | L  | L | L | L | D  | D | L | D | L | D  | L  | D | D | D  | D  |

| 2     | L  | L | L | D | d  | L | L | 1 | L | D  | L  | D | D | D  | D  |

| 3     | Ĺ  | L | L | D | d  | L | D | 1 | 1 | L  | L  | L | D | D  | D  |

| 4     | L  | L | d | D | d  | L | 1 | d | 1 | L  | 1  | L | L | D  | D  |

| 5     | L  | D | ď | D | d  | d | 1 | d | 1 | L  | 1  | L | L | L  | D  |

| 6     | L  | ī | d | D | ď  | d | 1 | d | 1 | d  | 1  | d | L | L  | L  |

| 7     | d  | i | d | 1 | d  | d | ì | d | 1 | d  | 1  | d | d | d  | L  |

Table 2.11: Final life-time table.

#### Interconnection Units Allocation

Resources with more than two outputs are merged into one data bus where possible.

This is possible only if both the connections are not used simultaneously. After that multiplexers are inserted where needed.

#### 2.3.3 Discussion

Many intermediate forms that are used in allocation have been discussed in this section. In FACET the allocation process starts from a scheduled straight code. A life-time table is built and a conflict graph is constructed. In HARP allocation also starts from a DFG and then a used/unused matrix is produced and then mutual correlation matrix is computed. A life-time table for compacting registers is obtained. It is concluded that flow graphs are ideal for the discussed allocation techniques. Moreover, it is observed that many additional intermediate forms are used to accomplish the allocation task. This is because allocation is usually conducted on all

hardware resources like: functional units (FUs), registers and interconnections.

### 2.4 Conclusion

In this chapter, several scheduling and allocation techniques and the intermediate forms used with them have been discussed.

Overall, the following statements can be made:

- Most intermediate forms are data flow based.

- Sequencing and concurrency are supported in all studied intermediate forms,

since hardware systems are inherently concurrent.

- Hardware designs are concurrent in nature. In other words, operations in hardware systems are executed as concurrent as possible.

- Some intermediate forms can highlight some hidden features of the system behavior that even the high-level specification language cannot express. For example, concurrency is not highlighted in the high-level specification language while it is clearly shown in some intermediate forms like CDFGs.

- This chapter shows the inter-dependencies between the various high-level synthesis tasks which is the basis of the classification that will be introduced in the next chapter.

• Each scheduling and allocation technique can operate on a specific intermediate form.

# Chapter 3

# Classification of Intermediate

# **Forms**

In this chapter we briefly overview high-level synthesis systems and their corresponding intermediate forms. From these high-level synthesis systems, a classification framework which classifies intermediate forms into two main classes: primary and secondary is proposed. Primary intermediate forms (PIF) and secondary intermediate forms (SIF), objectives and constraints of each system are highlighted.

## 3.1 Constraints

In the Webster dictionary "constraint" is defined as "compulsion". When the term speed constraint is mentioned, it means that the design is synthesized in such a way

so as to maximize its speed. The way of increasing speed can be achieved by making the design more parallel. This takes place while scheduling or by allocating fast hardware components, which takes place during allocation. Moreover, the design speed can be increased by avoiding using multiplexers, which will be on the expense of increasing the number of registers and interconnections. Another example is cost. Reducing cost means reducing the design area, which can be achieved by reducing the number of the hardware components (ALUs, registers, buses and muliplexers). Satisfying one constraint will usually be on the expense of another, that is why compromise solutions are considered. Constraints are important and heavily influence the scheduling and allocation algorithms.

## 3.2 Classes of Intermediate Forms

The high-level synthesis process starts as follows. The high-level language is first transformed into an intermediate form (DFG, CDFG). This translation is necessary because the high-level language is not a suitable format. Therefore, it is transformed to a processible format (intermediate form) that can capture the specifications of the high-level language and lend itself to synthesis tasks like scheduling and allocation. The intermediate form that results from transforming the high-level language is referred to as primary intermediate form (PIF). Synthesis tasks like scheduling and allocation extract a subset of the specification from the primary intermediate form

and build other intermediate forms referred to as secondary intermediate forms.

Therefore, intermediate forms can be classified according to the synthesis task they are used in. We classify intermediate forms into two main classes:

- Primary intermediate forms (PIF).

These are the ones produced from transformation, since they inherit all the system behavior and specifications from the high-level description.

- Secondary intermediate forms (SIF).

Those that extract a subset of the system specification from the PIF to perform a specific task in synthesis. These are usually used in scheduling and allocation.

High-level synthesis systems follow different approaches. Each high-level synthesis system synthesizes the input behavior under specific constraints to match specific objectives. In the following sections, some high-level synthesis systems are briefly surveyed. Primary intermediate forms (PIF), secondary intermediate forms (SIF), objectives and constraints of each system are highlighted when possible.

## 3.3 HAL Synthesis System

In HAL [22] the synthesis procedure starts with a high-level description. Some speed and cost constraints are imposed like: number of control steps and functional unit types. A scheduling technique called *force-directed* scheduling is used. This scheduling method reduces the number of functional units, registers and buses. It