**INFORMATION TO USERS**

This manuscript has been reproduced from the microfilm master. UMI

films the text directly from the original or copy submitted. Thus, some

thesis and dissertation copies are in typewriter face, while others may be

from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the

copy submitted. Broken or indistinct print, colored or poor quality

illustrations and photographs, print bleedthrough, substandard margins,

and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete

manuscript and there are missing pages, these will be noted. Also, if

unauthorized copyright material had to be removed, a note will indicate

the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by

sectioning the original, beginning at the upper left-hand corner and

continuing from left to right in equal sections with small overlaps. Each

original is also photographed in one exposure and is included in reduced

form at the back of the book.

Photographs included in the original manuscript have been reproduced

xerographically in this copy. Higher quality 6" x 9" black and white

photographic prints are available for any photographs or illustrations

appearing in this copy for an additional charge. Contact UMI directly to

order.

UMI

A Bell & Howell Information Company 300 North Zeeb Road, Ann Arbor MI 48106-1346 USA 313/761-4700 800/521-0600

# **Automated VHDL Composition from AHPL**

BY

## Faisal Mohammad Zafar Soleja

A Thesis Presented to the

FACULTY OF THE COLLEGE OF GRADUATE STUDIES

KING FAHD UNIVERSITY OF PETROLEUM & MINERALS

DHAHRAN, SAUDI ARABIA

In Partial Fulfillment of the Requirements for the Degree of

MASTER OF SCIENCE In

Computer Science

August 1996

UMI Number: 1381988

UMI Microform 1381988 Copyright 1996, by UMI Company. All rights reserved.

This microform edition is protected against unauthorized copying under Title 17, United States Code.

## KING FAHD UNIVERSITY OF PETROLEUM AND MINERALS DHAHRAN, SAUDI ARABIA

#### COLLEGE OF GRADUATE STUDIES

This thesis, written by FAISAL MOHAMMAD ZAFAR SOLEJA under the direction of his Thesis Advisor and approved by his Thesis Committee, has been presented to and accepted by the Dean of the College of Graduate Studies, in partial fulfillment of the requirements for the degree of MASTER OF SCIENCE in COMPUTER SCIENCE.

#### THESIS COMMITTEE

Jadiq Sait · M

Dr. Sadiq M. Sait (Chairman)

Dr. Muhammed S. Al – Mulhem (Co – Chairman)

Dr. Muhammad S. T. Benten (Member)

enartment Chairman

Dean, College of Graduate Studies

Date: 8-6-91

This thesis is dedicated to my three lovely daughters

Ayesha, Sara and Asma

#### Acknowledgments

First and foremost, all Praise is for Almighty Allah for having me guided at every stage of my life.

Acknowledgement is due to King Fahd University of Petroleum & Minerals for providing facilities and support to this work.

I am indebted to my thesis Chairman, Dr. Sadiq M. Sait, for his time, guidance and assistance. I am also highly thankful to my thesis Co-chairman and Department Chairman, Dr. Muhammed S. Al-Mulhem for all his sincere help and support. I would like also to place on record my great appreciation for the cooperation and suggestions extended by my committee members Dr. Muhammad S. T. Benten and Dr. Habib Youssef. My special thanks to all my thesis committee members, whose patience and forbearance have helped me to complete this work.

I wish to express my gratitude to my father, Dr. Mohammad Zafar Soleja, for his moral support, encouragement and motivation. To my mother and my sister I thank them for all their kind support. Lastly, I want to express my appreciation to my wife and my daughters for their tolerance and sacrifice.

## **Contents**

|   | Acl  | cnowledgements                                 | i    |

|---|------|------------------------------------------------|------|

|   | List | t of Tables                                    | v    |

|   | List | t of Figures                                   | vi   |

|   | Abs  | stract (English)                               | viii |

|   | Abs  | stract (Arabic)                                | ix   |

| 1 | Inti | oduction                                       | 1    |

|   | 1.1  | Motivation                                     | 4    |

|   | 1.2  | Literature Survey                              | 5    |

|   | 1.3  | Conclusion                                     | 9    |

| 2 | Har  | dware Description Languages                    | 11   |

|   | 2.1  | Introduction to Hardware Description Languages | 11   |

|   | 2.2  | AHPL and VHDL                                  | 12   |

|   |     | 2.2.1   | AHPL Overview         | · • • • • |     |       |     |   |       | • |   |   |   |   | 14 |

|---|-----|---------|-----------------------|-----------|-----|-------|-----|---|-------|---|---|---|---|---|----|

|   |     | 2.2.2   | VHDL Overview         |           |     |       |     |   |       |   |   |   |   |   | 18 |

|   |     | 2.2.3   | AHPL versus VHDL      |           |     |       |     |   |       |   |   | • | • |   | 19 |

|   | 2.3 | HDLs    | Analysis              |           |     |       |     |   |       |   |   | • |   |   | 20 |

|   | 2.4 | Summ    | ary                   |           |     |       |     |   | <br>• |   | • |   | • |   | 24 |

| 3 | Tra | nslatio | n of AHPL models      | to VHD    | L   |       |     |   |       |   |   |   |   |   | 25 |

|   | 3.1 | Transl  | ation Approach        |           |     | • •   |     |   |       |   | • |   | • | • | 26 |

|   | 3.2 | Mappi   | ng Concept            |           |     |       | •   |   | <br>• |   | • |   |   |   | 28 |

|   |     | 3.2.1   | Declarations          |           |     | • •   | •   |   |       |   | • |   |   |   | 28 |

|   |     | 3.2.2   | Processes             |           |     | • • • | • • |   |       |   | • | • |   |   | 34 |

|   |     | 3.2.3   | Blocks                |           |     | • • • | • . |   |       |   | • |   |   | • | 37 |

|   |     | 3.2.4   | State Machine         |           |     |       | • . |   | <br>• |   |   |   |   | • | 41 |

|   |     | 3.2.5   | Modeling Trailing Ed  | ge Transf | ers |       |     |   | <br>• |   | • |   |   |   | 41 |

|   |     | 3.2.6   | Modeling Transfers to | Buses .   |     |       |     |   |       |   | • |   |   |   | 42 |

|   |     | 3.2.7   | Modeling Conditional  | Transfer  | s.  |       |     | • |       |   | • | • |   |   | 44 |

|   | 3.3 | Mappi   | ng Summary            |           |     |       |     | • |       |   |   | • |   |   | 45 |

| 4 | The | Comp    | osition Process       |           |     |       |     |   |       |   |   |   |   |   | 47 |

|   | 4.1 | Compo   | osition Overview      |           |     | ·     |     | • |       |   | • | • |   |   | 48 |

|   | 4.2 | The A   | nalyzer               |           |     |       |     | • |       |   | • | • |   |   | 50 |

|   |     | 4.2.1   | The Analyzer Implem   | entation  |     |       |     |   |       |   |   |   |   |   | 52 |

| ٠ |   |

|---|---|

| 1 | v |

|   |      | 4.2.2   | State Table Generation      | 58  |

|---|------|---------|-----------------------------|-----|

|   | 4.3  | The C   | Composer                    | 64  |

|   |      | 4.3.1   | The Declaration Transformer | 66  |

|   |      | 4.3.2   | The Controller Generator    | 68  |

|   |      | 4.3.3   | The Data Path Builder       | 71  |

|   |      | 4.3.4   | Template Compiler           | 74  |

|   | 4.4  | VHDI    | Template                    | 74  |

|   |      | 4.4.1   | Control Path Emulation      | 78  |

|   |      | 4.4.2   | Data Path Mapping           | 82  |

|   |      | 4.4.3   | CLU Mapping                 | 85  |

|   | 4.5  | Utility | Library                     | 87  |

|   | 4.6  | An Illi | ustrative Example           | 87  |

|   | 4.7  | Summ    | ary                         | 91  |

| 5 | Con  | clusio  | n and Future Work           | 94  |

|   | App  | endix   | A                           | 98  |

|   | App  | endix   | В                           | .00 |

|   | Bibl | liograp | phy 1                       | .08 |

## List of Tables

| 2.1 | Comparison Analysis of HDLs                                   | 23 |

|-----|---------------------------------------------------------------|----|

| 3.1 | AHPL Declaration Elements and their VHDL Counter-parts        | 31 |

| 3.2 | Basic AHPL Modeling Elements/Features and their VHDL Counter- |    |

|     | parts                                                         | 46 |

| 4.1 | Declaration Information Table.                                | 54 |

| 4.2 | State Control Table                                           | 55 |

| 4.3 | Register & Bus Transfers Structure Table                      | 56 |

## List of Figures

| 2.1 | HDL Time Line                           | 13 |

|-----|-----------------------------------------|----|

| 2.2 | AHPL Description of a Multiplier        | 15 |

| 2.3 | Block Diagram of 4-bit Multiplier       | 16 |

| 3.1 | Data and Control Parts                  | 27 |

| 3.2 | Entity Interface Declaration            | 30 |

| 3.3 | Architectural Specification             | 32 |

| 3.4 | Process Statement with Sensitivity List | 36 |

| 3.5 | Process Statement with Wait Statement   | 38 |

| 3.6 | Model of D_flipflop Using Guarded Block | 40 |

| 3.7 | Trailing Edge Implementation            | 43 |

| 4.1 | The Composition Process Steps           | 49 |

| 4.2 | The Analyzer Block Diagram              | 51 |

| 4.3 | FSM Diagram of AHPL Model               | 53 |

| 4.4 | Sample Lex Code                         | 59 |

| 4.5  | Sample Yacc Code                         | 60 |

|------|------------------------------------------|----|

| 4.6  | The Composer Block Diagram               | 65 |

| 4.7  | Algorithm for Declaration Transformer    | 67 |

| 4.8  | Algorithm for Controller Generator       | 69 |

| 4.9  | Algorithm for Data Path Builder          | 72 |

| 4.9  | Algorithm for Data Path Builder (cont)   | 73 |

| 4.10 | Template Style                           | 76 |

| 4.10 | Template Style (cont)                    | 77 |

| 4.11 | Generic Control Block                    | 80 |

| 4.12 | Sample Control Block                     | 81 |

| 4.13 | Generic Data Block.                      | 83 |

| 4.14 | Sample Data Block                        | 84 |

| 4.15 | CLU Mapping                              | 86 |

| 4.16 | Composed VHDL Model of Multiplier        | 88 |

| 4.16 | Composed VHDL Model of Multiplier (cont) | 89 |

| 4.16 | Composed VHDL Model of Multiplier (cont) | 90 |

| 4.17 | VHDL Simulated Output                    | 92 |

#### Abstract

Name:

Faisal Mohammad Zafar Soleja

Title:

Automated VHDL Composition from AHPL

Major Field:

Computer Science

Date of Degree: August 1996

Hardware description languages (HDLs) have been widely used for documentation, communication and verification. They have also been used as input specification languages to Design Automation (DA) systems which synthesize VLSI layouts. AHPL is an HDL that has been in use for the past three decades in modeling digital systems. Recently a language called VHDL (VHSIC Hardware Description Language) developed under the auspices of the United States Department of Defense Very High Speed Integrated Circuits Program, is rapidly emerging as the next generation Design Automation Language. However, because of its large size and sophistication, VHDL is a difficult language to learn and master. On the other hand, AHPL is a very concise language that can be mastered within few hours. The objective of this research is to develop a tool that will assist designers quickly learn and model in the VHDL language. In this thesis, we present a tool for the automatic composition of VHDL descriptions from their equivalent AHPL specifications. Central to the composition algorithms is a template which is the skeleton of a generic VHDL model consisting of a small subset of VHDL constructs that are sufficient to capture VHDL equivalent descriptions of any input AHPL model.

Master of Science Degree

King Fahd University of Petroleum and Minerals

Dhahran, Saudi Arabia

August 1996

#### خلاصة الرسالة

الاسم: فيصل محمد ظفر صوليجا

عنوان الرسالة: آلية VHDL المؤلفة من AHPL

التخصص: علم الحاسب الآلي

تاريخ الشهادة: اغسطس ١٩٩٦م

تستخدم لغات وصف الدوائر (HDLs) غالبا في التوثيق والاتصال و التحقق ، وكذلك تستخدم كلغة توصيف مدخلة الى أنظمة التصميم المآلي (DA) المستخدمة في توليف نماذج الدوائر المتكاملة ذات النطاق الواسع جدا (VLSI). وخلال العقدين الماضيين استخدمت لغة (AHPL) - وهي من لغات وصف الدوائر (HDL) - في نمذجة الأنظمة الرقمية. ومنذ عهد قريب تم تطوير لغة اسمها VHDL (لغة VHSIC) لوصف الدوائر) تحت رعاية برنامج وزارة الدفاع الامريكية لتطوير الدوائر المتكاملة ذات السرعات الفائقة. وهذه اللغة تأخذ طريقها بسرعة كلغة الجيل التالي لأنظمة التصميم الآلي. ولكن بسبب مدى ضخامتها وتطورها جعلت من VHDL لغة صعبة التعلم و الابداع. وبالمقابل فان AHPL لغة مختصرة يمكن التفنن فيها خلال ساعات قليلة. اللهدف من هذا البحث هو تطوير أداة تسهل على المصممين سرعة التعلم و الابداع في لغة المكافئة لها. والجزء الرئيس في الخوارزمية المقترحة هو قالب المعايرة وهو مخطط هيكلي المكافئة لها. والجزء الرئيس في الخوارزمية المقترحة هو قالب المعايرة وهو مخطط هيكلي لاستخلاص وصف VHDL توليدي. يتكون من مجموعة جزئية صغيرة من تركيبات VHDL كافية المؤلف المقترح.

درجة ماجستير علوم جامعة الملك فهد للبترول والمعادن الظهران, المملكة العربية السعودية اغسطس ١٩٩٦م

## Chapter 1

#### Introduction

In the era of VLSI, the size and complexity of digital systems have grown tremendously. To effectively and efficiently design such systems many computer-aided design tools were introduced and among them was the development of the Hardware Description Languages (HDLs). Since then, HDLs have been extensively used to describe hardware for the purpose of simulation, modeling, testing, design, and documentation of digital systems. At first, the use of formal HDLs was confined to academic circles. They were used in the teaching of computer architecture concepts as well as the verification of new hardware through simulation. HDLs were not commercialized until early 1980's. Since then, they saw a wide use as interface between tools, as documentation of new designs, as interfaces to design databases, and as interfaces between IC manufacturers. The commercialization of HDLs brought with it the standardization wave. Standardization was motivated by several reasons, most

important among them were:

- the need to provide a common interface between CAD tools, this is to answer the portability issue,

- the need to have a multi-purpose language, that is, a language that is not confined to a single level of circuit description, and

- the requirement for a language to support the hierarchical description of large designs; this is indicated by the increasing level of density as well as complexity of new VLSI circuits.

It is this standardization effort that led to the advent of the VHDL language. VHDL is now the most important standard in the CAD community mainly because it satisfies the three requirements listed above [DG86]. Furthermore, VHDL is supported by efficient hierarchical simulators from the system level to the gate level and is becoming the language of choice for government, industry and academia participating in electronic research, business, and education.

The advent of VHDL has provided a foundation for the communities of design automation, design and test, and manufacturing, to reduce product cost through improved designer productivity and maintenance capabilities [Wax86]. A standard hardware description of a design has enabled developers of design workstation, test equipment, and design automation software to provide common data interface among their tools. Standard human-readable description of design data facilitates

exchange of data among designers, enabling them to work effectively with design tools [LSU89]. VHDL not only provides the feature for suitable descriptive medium but also a design tool. It also provides a standard textual means of description for hardware components at abstraction levels ranging from the logic gate level to digital system level [LMS86]. It provides precise syntax and semantics documentation for the hardware components, enabling design transfer both within and among organizations.

Another hardware description language that enjoyed and still enjoys widespread use (mostly in academia) is the AHPL language [HDL92a, HP73]. AHPL is a hardware description language based upon the notational conventions of APL. AHPL was developed in an academic environment to teach digital system design. Its basic structural similarity to high-level programming languages makes it accessible to wider class of users than would be the case with a more specialized hardware language. AHPL is neither a standard nor a multipurpose language. It is a language for the description of digital system at the Register Transfer level (RTL). AHPL is the easiest hardware language to teach/learn among all existing HDLs. VHDL on the other hand, can be quite intimidating for a first time user.

This thesis presents the design of a Composer which automatically generates a VHDL model from an equivalent AHPL input model. This composition is achieved in two stages with the help of a especially designed template and an external library of predefined functions. The Composer accurately obtains a VHDL model from any

AHPL input model. Both models are equivalent in their function and the level of description of hardware (RTL level) [SYBS93, SYBS94].

#### 1.1 Motivation

The principle motivation for the development of such a Composer is three-fold:

- 1. Rapid prototyping of VHDL models.

- 2. Easy migration from AHPL-like languages to VHDL.

- An educational tool to aid in the teaching of a large HDL such as VHDL (with a large variety of features and constructs).

The Composer will also help reverse engineer the high-level synthesis process. The AHPL language is a purely RTL language. The composition of VHDL models from their AHPL counterparts will provide insight into how best one can perform high-level synthesis of digital systems from VHDL descriptions. The composition process gives a good understanding of how one can perceive the hardware correspondence from VHDL model.

VHDL is a multi-purpose HDL and is among the hardest HDLs to master. On the other hand, AHPL is a single purpose language, is relatively small and is among the easiest to learn. We believe that the *Composer* developed in this thesis will assist AHPL modelers to easily migrate and learn VHDL. Furthermore in academia as well as for novice VHDL users the Composer can play the beneficial role of a computer aided teaching tool in helping users quickly learn RTL modeling in VHDL. More experienced users can also find the Composer helpful to quickly generate a correct RTL-level VHDL model, so that they only need to worry about generating VHDL architectural descriptions at higher levels (behavioral, timing, performance issues).

The hardware design implemented using AHPL are usually small and concise. In contrast VHDL code tends to be verbose and lengthy due to the strong data-typing and data declaration features of VHDL for every element to be declared before use [NS86]. Although this feature is beneficial for comprehensive design documentation and readability, it discourages designers to migrate to VHDL. The *Composer* has ability to lessen burden of writing the VHDL code by generating entire architecture of the design including the initial declaration and the correct syntactic execution statements.

#### 1.2 Literature Survey

Early work in this area mainly concentrated on methodology for using VHDL to model design at different levels. The facility of VHDL to describe hardware at several abstraction levels from the logic gate to the system level [LSU89] was encouraging factor for hardware designer to start modeling in VHDL. The increasing role of

VHDL as the preferred design language also encouraged researchers to use VHDL for high-level synthesis. Previous attempts at synthesizing from VHDL did not fully take the advantage of the VHDL capability to represent hardware design at varying levels.

VHDL provides suitable design environment for specifying, simulating and synthesizing digital hardware [NBD92]. The use of VHDL for synthesis has presented some problems as VHDL was designed mainly as a documentation language. As a result, researchers have defined various subsets for synthesis.

Although a lot of attention has recently been given to synthesis from other forms of hardware representation, the process of synthesis is not new. A great deal of useful work has been contributed on synthesis from behavioral specification [RKDV92], register transfer [NS90], and structural [LG89] level description. Interested readers are referred to [WC91] for an extensive survey of the research and development of synthesis systems.

In early development of behavioral synthesis, a VHDL Synthesis System (VSS) [LG89] was implemented to describe the methodology to generate structural design. Behavioral synthesis is defined as the translation of a behavioral description into a structural description. In VHDL, designs can be described in several ways and at several different levels of abstraction. The authors of the VSS introduced modeling styles that will allow for efficient generation of high quality designs. This synthesis system supports four design models: combinational logic, functional description,

register transfer description, and algorithmic designs. An interesting modeling approach was defined for describing the state machine design and to specify the operations to be processed for each machine state. Each state comprises one or more triplets that specify the actions to be performed. Each triplet is made up of a condition, a next state, and a set of operations. The VHDL guarded block statements are used to represent each machine state of a design and the block guard to specify the clocking mechanism.

In later development the concept of templates for synthesis from VHDL [NS90] was introduced. Two different VHDL templates for synthesis description styles were implemented: one for dataflow level of description and the other at more behavioral level. For both of the templates a general synthesis subset of VHDL construct was defined. This subset was used to design and describe the clocking schemes. The clocking mechanism used in each of the template was: explicit clocking in which a variable is used to keep track of the present state; and implicit clocking in which a boolean vector is used to determine the processing step. Although both of the templates are synthesizable and a hardware correspondence exists for them, their synthesis style does not fully provide the facility to easily define the complete state table of a finite state machine.

In [JW89], a prototype system called VCOMP was developed with the intention to simplify the introduction of VHDL for novice hardware designers. VHDL Composition System (VCOMP) is an environmental tool to provide the functions of a

tutorial and design developer for beginners in VHDL. This system allows users to effectively create hardware description of a system and formulate test vectors for simulation to verify correctness of the design. In general this system was confined in helping the hardware designer to learn the syntax of VHDL and to produce code for simulation and testing.

The VHDL language is designed to be efficiently simulated. Traditionally, designers have performed simulation with high-level simulation languages or in ad-hoc fashion by writing custom simulators in C or some other programming language. VHDL enables simulation across many different levels of abstraction. Although, VHDL presents many syntactic constructs for high-level system simulation [NS86], VHDL offers tremendous advantage of mixing high-level simulation with low-level simulation. This ability of VHDL to do simulation at multilevel allows rapid-prototyping process for system designs [SB92].

Simulation for VHDL models has often perceived to be a performance disadvantage compared to simpler and better established hardware description languages due to magnanimity and complexity of the language. Many VHDL simulators have been implemented to accelerate simulation performance by means of optimizing compilation and parallel simulation [WS92]. New compilation techniques are available to reduce runtime complexity and to promote concurrency in the VHDL models.

In view of VHDL's growing use and pervasive impact on electronic technology, literature survey has revealed that extensive work is being done in VHDL-related

research and development. Early work concentrated in demonstrating the variety of design approaches available in VHDL. Later work concentrated in more serious usage aspect of high-level synthesis from VHDL specification. Much useful work was done in synthesis of hardware correspondence from VHDL model but it was confined to subset of VHDL constructs. To lessen the burden of synthesis, the concept of templates was introduced. Templates provide a variety of styles for modeling in VHDL.

#### 1.3 Conclusion

In this opening chapter, the significance of the thesis work was presented. The basic objective of the thesis was, quite simply, to design and implement a Composer that will assist in transformation of AHPL specification to its functionally corresponding equivalent VHDL model. The primary motivation for the development of the Composer was to provide the tool to quickly and easily migrate to VHDL language for people already familiar with AHPL-like languages. The success and the widespread use of the VHDL has encouraged hardware designers for using VHDL for high-level synthesis. The composition of VHDL model from its AHPL counterpart gives the opportunity to describe as how best one can perform high-level synthesis of digital system from VHDL description. The composition process provides a better

understanding of how one can perceive the hardware design of a VHDL model.

In the following chapter an overview of Hardware Description Languages (HDL) is presented. This is followed by a series of chapters describing in detail the whole composition process. The thesis ends with the conclusion chapter that summarizes the work.

## Chapter 2

## Hardware Description Languages

This chapter present the introductory overview of Hardware Description Languages (HDL). The chapter starts with the definition of HDL and specifies some of the current usages of HDL. This is followed by the general overview of the two concerned HDL namely, AHPL and VHDL. Also included in the chapter is a comparison analysis study of nine well known HDLs and a summary of their features.

## 2.1 Introduction to Hardware Description Languages

Hardware Description Language (HDL) is a notational medium for the precise capture of certain features of a hardware design. They are extensively used for the purpose of simulation, modeling, testing, design, and documentation of digital design. These languages provide a convenient and compact format for representing the output of various design stages.

Hardware description languages basically comprise of a set of symbols and notations for the representation of digital circuits. Some HDL also have the ability to model the hardware at one or more levels of abstraction. HDL software includes simulation programs for the hardware design verification, and synthesis programs for the facility for automatic hardware generation [Nav93].

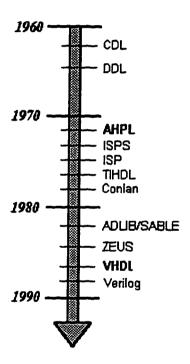

Today's hardware description languages benefit from the efforts of designers of hardware description languages dating back to the mid 1960s. Figure 2.1 shows the evolution of hardware description languages over the last few decades. In following section an interesting look is provided at two of these HDLs, namely AHPL and VHDL. Finally in the last section a comparison summary is included of AHPL and VHDL against some other well known HDLs.

#### 2.2 AHPL and VHDL

In this section a brief overview of both AHPL and VHDL is presented and discussed. The section is not intended to be a tutorial on either hardware description language. Interested readers are referred to [HP73] for details on AHPL, and to [Arm89, VHD88, Per93, Nav93, LSU89] for details on VHDL. The sole purpose here is to briefly introduce both languages and highlight some of their key elements which

Figure 2.1: HDL Time Line.

are necessary for the description of the Composer.

#### 2.2.1 AHPL Overview

AHPL is a hardware description language for describing the hardware at RTL level. AHPL came into existence in academic environment after the need arose for an easily manageable medium to teach digital system design. Since last two decades it has served a useful tool for teaching computer organization. The AHPL language is based on a subset notation of APL with many special added features to describe hardware specific details. The language is powerful enough to describe highly complex digital systems in an elegant way, yet it is the most compact and easiest to learn of all hardware description languages.

AHPL was designed as a hardware synthesis language and, therefore, is timestep oriented. In this language data assignment to registers are done synchronously

by an implicit clock. AHPL does not provide any support for asynchronous hardware designs. In AHPL, digital designs are described using interactive concurrent

modules. Iterative combinational networks such as adders, decoders, etc., can be

described as Combinational Logic Units (CLUs). The language does not support

timing mechanism and assignments of values to buses have immediate effect, while

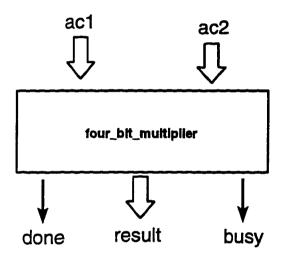

those to registers happen at the trailing edge of the clock. Figure 2.2 shows an

AHPL description of a 4-bit multiplier of Figure 2.3 that will be later used as the

vehicle to illustrate the composition system.

```

MODULE

: MULTIPLIER.

MEMORY

: AC1[4]; AC2[4]; COUNT[2]; EXTRA[5]; BUSY.

EXINPUTS

: DATAREADY; CLOCK; RESET.

EXBUSES

: INPUTBUS[8].

OUTPUTS

: RESULT[8]; DONE; BUSYOUT.

CLUNITS

: INC[2]<: INCR{2}.

CLUNITS

: ADD[5] <: ADDER\{5\}.

BODY SEQUENCE: CLOCK

AC1,AC2 \le INPUTBUS; EXTRA \le 50; => (^DATAREADY)/(1).

1

2

BUSY<=1$1; => (^AC1[3])/(4).

EXTRA \le ADD[0:4](EXTRA[1:4];AC2).

EXTRA,AC1<=1$0,EXTRA,AC1[0:2]; COUNT<=INC(COUNT);

=> (^(&/COUNT))/(2).

RESULT=EXTRA[1:4],AC1; DONE=1$1; BUSY <=1$0; =>(5).

ENDSEQUENCE

BUSYOUT=BUSY;

CONTROLRESET(RESET)/(1).

END.

```

Figure 2.2: AHPL Description of a Multiplier.

Figure 2.3: Block Diagram of 4-bit Multiplier.

As can be observed in Figure 2.2 every AHPL description consists of basically three parts:

- a declaration part

- procedure part

- non-procedural part

The declaration part consist of description of all the registers and buses. The procedural part describes the state machine, and this is followed by a non-procedural part. Referring to Figure 2.2 the numbered steps between the keywords SEQUENCE and ENDSEQUENCE form the procedural part defining the states of the sequential machine. In this part, a statement is active only when the machine is in the corresponding step (state). A step may have zero or more transfer or connection statements, followed by a conditional or unconditional branch statements. The destination of a transfer statement is always a memory element and that of the connection is non-memory like a bus or a set of output lines. A connection is active throughout the corresponding control step whereas a transfer is assumed to take place only at trailing edge of the clock in that step. The step numbers and branch statements define the sequencer of the control unit of the module. The non-procedural part follows the keyword ENDSEQUENCE. Statements in this part are always active regardless of the state of the control sequencer. Permanent connections between elements are to be described in this segment.

#### 2.2.2 VHDL Overview

VHDL is a multipurpose hardware description language supporting several abstraction levels of design description, from the logic/gate level to the system/behavioral level. In VHDL the hardware objects are expressed using design constructs as either design entity, configuration, or package, with the internal code being declaration, specification, expressions, and statements.

The primary abstraction element in VHDL is the design entity since it represents the logic circuits from the very complex system to simple circuit units. The design entity consists of the interface description and one or more architectural bodies. The interface description specifies the entity name and defines the inputs and outputs of the entity design for the communication with the outside world. The architectural body gives the internal structure of the object as structural description, data flow description, a behavioral description, or a mixture of these.

The configuration construct is used to bind a named component to a specific architecture of a specific design entity. It is also useful to link subcomponents used in an architecture to lower level entity/architectures. The package concept originating from Ada provides a mechanism for encapsulating definitions and utility functions. The package contains a collections of declarations and programs that are frequently used. This construct (together with many others such as user defined data-types) is unique to VHDL among other HDLs.

The entities and component instantiations are primarily used for the structural decomposition of the system being modeled. While processes, subprograms, package, etc., are for the purpose of decomposing the behavior of the system.

In VHDL, sequential and concurrent circuit models are represented by 'process' and 'block' design elements respectively. Statements within a process are executed in sequence. However, each statement within a block is considered as a process, that is, all the statements of the block are executed whenever the block is allowed to run. The language has three classes of objects: constants, variables, and signals. Variables have no direct hardware correspondence whereas signals have equivalence in hardware. When a signal has more than one source it is defined with a resolution function to determine its correct source. VHDL supports a variety of data types and option for user-defined types. Finally VHDL supports the facility to maintain multiple design libraries to store user defined and system defined primitives and descriptions. It also allows the description of synchronous as well as asynchronous systems, and data transfers can be on the rising or falling edge of the clock.

#### 2.2.3 AHPL versus VHDL

AHPL is simple and concise hardware description language. Beside being one of the smallest language, it provides a powerful capability to describe complex hardware design. AHPL has its limitation but it is good language to introduce for beginners to hardware design.

VHDL provides a foundation for the communities of design automation, design and test, and manufacturing to reduce product cost through improved designer productivity and maintenance capabilities. Being the standard hardware description language VHDL provides the designer and developers a common data interface among their tools. VHDL's rich features make it suitable not only as a descriptive medium but also as a design tool.

#### 2.3 HDLs Analysis

In this section a short analysis of nine well known hardware description languages is presented. The analysis is based on the prominent features available by these nine hardware description languages. The nine selected hardware description languages are:

- IDL Interactive Design Language

- TI-HDL Texas Instrument Hardware Description Language

- CDL Computer Design Language

- AHPL A Hardware Programming Language

- ZEUS Hardware Description Language

- CONLAN A Consensus Language

- TEGAS Test Generation and Simulation

- ISIS Instruction Set Processor Specification

- VHDL VHSIC Hardware Description Language

A detailed overview of AHPL and VHDL was presented in an earlier section. For brief outline of other HDLs, readers are encouraged to review [AWS86, HDL92a, HDL92b]. The comparison analysis for the nine HDLs was conducted on the basis of the following seven criteria:

- Scope the range of hardware: the language support to describe and design at different levels.

- Management of design: support for different design methodologies, design abstraction and resuability.

- Timing description: capability to include timing mechanism in a design hierarchy and abstraction.

- Architecture description: capability to describe at different levels of design details. Also the control structures for statement execution.

- Description of a design interface: availability of a mechanism for defining external interface to design description.

- Description of a design environment: support for design tools and ability for environment definition.

- Language extensibility: flexibility for user-defined extension and support for future advances.

The comparison analysis of the nine HDLs is summarized in Table 2.1. In short all evaluated languages at least support gate-level design and synchronous sequential design. Most of the languages support hierarchy, modularity and libraries. Architectural description is possible in most of the languages. All of the languages can support more than one technology and more than half support multiple methodologies.

All these excellent hardware description languages in industry today cover various aspects of hardware design and description, but none matches VHDL's capabilities. The analysis has shown that no current hardware language capabilities, shortcomings and other characteristics had been overlooked in developing VHDL. VHDL has proven to be modern language that is complete and comprehensive. Furthermore, all the salient features of AHPL are available in VHDL, thus AHPL in terms of features forms a subset of VHDL.

| Features Supported         | IDL                      | TI-<br>HDL | CDL | AHPL        | ZEUS     | CON-<br>LAN | TE-<br>GAS | ISPS        | VHDL |

|----------------------------|--------------------------|------------|-----|-------------|----------|-------------|------------|-------------|------|

| Scope-range of hardware:   | Scope-range of hardware: |            |     |             |          |             |            |             |      |

| Digital-system design      | x                        | x          |     | ×           | X        | ×           | x          | x           | x    |

| Gate-level design          | x                        | x          | x   | x           | x        | x           | x          | x           | x    |

| Combinational design       |                          | x          |     | x           |          | x           | x          | x           | x    |

| Synchronous design         | x                        | x          | x   | x           | x        | x           | x          | x           | x    |

| Asynchronous design        |                          | x          |     |             |          | x           | x          | x           | x    |

| Mixed-mode                 |                          | x          |     |             |          |             | x          |             | x    |

| Management of design:      |                          |            |     |             |          |             |            | <del></del> |      |

| Hierarchy                  | ×                        | x          |     | x           | <u>x</u> | x           | х          | x           | x    |

| Modularity                 | x                        | x          |     | x           | x        | x           | x          | x           | x    |

| Incremental compile        |                          | x          |     |             | x        |             |            | -           | x    |

| Libraries                  | x                        | x          |     | x           | x        | x           | x          | x           | x    |

| Data abstraction           |                          |            |     |             | x        | x           |            |             | x    |

| User type conv             |                          |            |     |             |          |             |            |             | x    |

| Alternate description      |                          |            |     |             |          |             |            |             | x    |

| Reusable design            | x                        | x          |     | x           | x        | x           | x          | x           | x    |

| Timing description:        |                          |            |     |             |          |             |            |             |      |

| Timing at all levels       | х                        | x          |     | ×           | х        | ×           | x          | x           | ×    |

| Specify timing data        |                          | x          |     | x           |          | x           | x          | x           | x    |

| User-defined data          |                          | x          |     | x           |          | x           | x          |             | x    |

| Timing constraint          |                          | x          |     |             |          |             | x          |             | x    |

| Propagation delay          | x                        | x          |     | x           |          | x           | x          | x           | x    |

| Architectural description: |                          |            |     | <del></del> |          |             |            |             |      |

| Algorithmic description    | х                        | х          |     | x           | x        | x           | ×          | x           | х    |

| Architecture description   | x                        |            | x   | x           | x        | x           | x          | x           | x    |

| Parallelism                | x                        |            | x   | x           | x        | x           | x          | x           | x    |

| User assertions            |                          |            |     |             |          | x           |            | x           | x    |

| Generic components         |                          | x          |     |             | x        | x           | x          |             | x    |

| Recursive structures       |                          |            |     | x           | x        | x           |            |             |      |

| Interface description:     |                          |            |     |             |          |             |            |             | -,   |

| Explicit interface         |                          | х          |     | X           | ×        | x           | x          | X           | X    |

| Strongly typed interface   |                          |            |     |             | x        | x           |            |             | x    |

| Design environment:        |                          |            |     |             |          |             |            |             |      |

| Environment information    |                          |            |     |             |          |             |            | x           | x    |

| Language extensibility:    |                          |            |     |             |          | <del></del> |            |             |      |

| User-defined data types    |                          |            |     |             | x        | x           |            |             | x    |

| Design tool support        |                          |            |     |             |          | x           |            | x           | x    |

| Multiple technologies      | x                        | x          | x   | x           | x        | x           | x          | x           | x    |

| Multiple methodologies     | х                        | x          |     | х           |          | x           |            | х           | х    |

Table 2.1: Comparison Analysis of HDLs.

# 2.4 Summary

This chapter presented introductory material of hardware description languages. The intention of the first part of the chapter was to give an overall understanding of the concept of hardware description language and their use in design environment. The second part of the chapter presented two hardware description languages, namely AHPL and VHDL. A brief overview of these languages and their many salient features were highlighted. In the last part nine well-known HDL language were selected and a comparison analysis was summarized.

# Chapter 3

# Translation of AHPL models to

# VHDL

The intent of this chapter is to provide a general knowledge to understand the composition process. The first part of the chapter describes the translation approach

that was adopted in order to analyze the AHPL specification and to generate its corresponding equivalent VHDL model. The remaining part of this chapter is devoted

to present and describe the VHDL construct that are available for the purpose of

composing VHDL model. A comprehensive study was conducted to find the most

suitable set of constructs that will best describe the AHPL specification.

In the next chapter the *composition process* is presented using the concept learnt from this chapter.

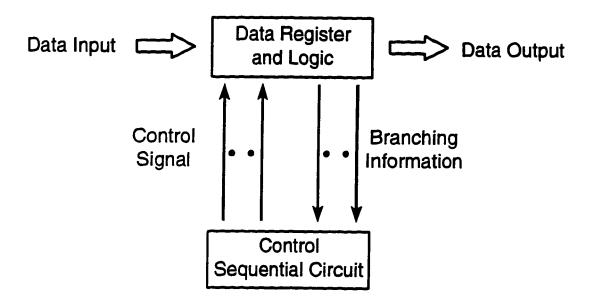

## 3.1 Translation Approach

AHPL is based on the fact that any digital system can be partitioned into a data part and a control part as shown in Figure 3.1. The data part consists of registers, buses, CLUs and some basic gates. The control part consists of logic which provides signals to control the operations in the data part. Additionally, the sequencing of control is influenced by the branching information fed back from the data part. Generally, the major role of the control part consists of a schedule defining each operation in the data part and determining the ordering and timing in which these operation take place. Similar to other HDLs, AHPL has its own set of conventions for transfers, connections, register indexing, etc.

VHDL does not require separation between the data flow and the control flow. If the designer/modeler desires to separate between data and control, he must explicitly incorporate control mechanism in the design model. A convenient method is by including guard in all the statements (a guarded statement is executed when the guard condition is true while all non-guarded statements as well as blocks whose guards are true are executed in parallel).

Conventionally, in AHPL, all transfers into registers take place at the trailing edge of the clock pulse. Also, transitions between states of the finite state machine take place at the trailing edge. However, transfers to buses or input/output lines, called *connections*, are active for the entire duration of the clock pulse.

Figure 3.1: Data and Control Parts.

In the following sections a detail survey is made on some of the constructs available in VHDL. These constructs are introduced, with the justification that the essential features of AHPL can be mapped to its equivalent VHDL model. The realization of some of the important basic AHPL elements and features with their possible counter-parts is summarized at end of this chapter.

# 3.2 Mapping Concept

In this section several concepts are presented that are needed to be understood for purpose of realization of VHDL model from the AHPL model. These ideas are used in the building of the *Analyzer* and the *Composer* that are described later in the next chapter. Also included is a description of some of VHDL constructs that are required for the accomplishment of the task of translation.

#### 3.2.1 Declarations

In VHDL, many features are available to facilitate the description of components and systems. A digital device in VHDL is represented as a design entity. In its simplest form, a design entity consist of two parts:

- an entity declaration

- an architecture body

As shown in Figure 3.2, the entity declaration begins with the keyword entity and defines the interface to describes the inputs/outputs (I/O) ports of the component, that is, what the outside world sees and communicates. Ports define communication channels between design entities and the outside world. A port definition involves description of its mode and type. The port's mode specifies the direction of information flow through the port. A port type specifies the set of values a port may assume.

The declarations of INPUTS, OUTPUTS, EXINPUTS, EXOUTPUTS and EXBUSES in AHPL module are taken care of by the interface description of the entity. These are declared as ports along with associated input or output mode. Registers declared as MEMORY in AHPL, and internal BUSES, are declared as signals inside the section that models the architecture. Table 3.1 gives the summary of how AHPL declaration elements are realized in VHDL.

Other external characteristics of a component, such as timing dependencies, can also be included in the entity interface of the component. The name of the component comes after the keyword entity and is followed by keyword is.

As shown in Figure 3.3, an architecture specification begins with the keyword architecture, which describe a possible internal functionality of the entity. This functionality depends on the input-output signals and other parameters that are specified in the entity interface declaration. A functional description of the component starts after the keyword begin.

entity component\_name is input and output ports. physical and other parameters. end component\_name;

Figure 3.2: Entity Interface Declaration.

| AHPL Element | VHDL Object                       |

|--------------|-----------------------------------|

| Input        | Port in entity interface in mode  |

| Output       | Port in entity interface out mode |

| Exinput      | Port in entity interface in mode  |

| Exoutput     | Port in entity interface out mode |

| Exbuses      | Port in entity interface in mode  |

| Memory       | Signal in architecture body       |

| Buses        | Signal in architecture body       |

Table 3.1: AHPL Declaration Elements and their VHDL Counter-parts.

architecture identifier of component\_name is declarations.

### begin

specification of the functionality of the component in terms of its input lines and as influenced by physical and other parameters end identifier;

Figure 3.3: Architectural Specification.

In VHDL several architectural specifications with different identifiers can exist for one component with a given entity interface declaration. An architecture description could have three general styles of description: structural, dataflow, and behavioral or an unrestricted combination of all three. Structural description captures the schematic view of hardware and consist primarily of interconnected components. Dataflow description, a little more abstract, specifies data transform being performed in terms of concurrently executing RTL statements. Behavioral description, the most abstract, specifies data transforms in terms of algorithms for composing output responses to input changes. In this work the composed VHDL description that is produced is at the dataflow/RTL level, which is at the same level as the input AHPL description.

In VHDL, separation of the entity external interface from the internal architecture is a convenient feature. The entity structure can be viewed as describing the black box property and the architecture body as the glass box property.

In the declaration of signals in the architecture body it is often required to be declared as resolved signal. A signal which has more than one source is called a resolved signal. In such cases resolved signal must have a resolution function associated with it to resolve multiple sources into a single value for the signal. The resolution function is invoked every time the value of the resolved signal is updated. If two sources are driving the signal, then the resolution function is invoked with array of length two which contains the values of the two sources. Based on the

definition of the resolution, the returned result value is obtained by tying together the input source values. The resolution function used for the implementation of the *Composer* is a simple Wired\_Or function which collects the values sent from all the input sources and applies the OR function to generate a single value.

#### 3.2.2 Processes

The process construct of VHDL represents the fundamental method by which concurrent activities of a digital system are modeled. All processes are executed in parallel. A process statement has a declarative and statement parts. All the variables and constant objects are declared in the declaration part and these objects are initialized only once at the beginning of a simulation run. The statement part of a process is sequential and is always active. Each process statement defines a specific action, or behavior, to be performed. This behavior is defined by sequentially ordered execution statements in the process.

Statements in a process continue to execute until they are suspended. Once suspended, a process can be reactivated. One way a process can be reactivated is by designating a maximum time for the process to remain suspended. A common mechanism for suspending and subsequently conditionally activating a process is the use of sensitivity list. Following the keyword process, a list of signals in parentheses can be specified. This list is called sensitivity list, and the process is activated when an event occurs on any of these signals. When the program flow reaches the last

sequential statement, the process becomes suspended, although alive, until another event occurs on a signal that it is sensitive to. Figure 3.4 shows the example of a process that is controlled implicitly by the sensitivity list. This process, named Or\_Process, has a sensitivity list of two signals, in1 and in2. Whenever any change of state happens for any of these signals, the process is activated, and the assignments in the statement part of the process are executed. In this case the output signal will obtain the result of the 'or' of the values of the signal in1 and in2.

Alternatively, the activation and suspension of the process can be controlled by a single construct called the wait statement. When the wait statement is executed inside a process, the process suspends and the conditions for its reactivation are set. There are three different kinds of conditions: timeout, condition, and signal sensitivity, and these kinds of conditions can be mixed together in the wait statement. In the timeout form, a maximum delay for the process to be suspended is defined and when the delay expires, the process is reactivated. In the second form, a condition must be true before the process can be resumed. The final form provides a list of signals which is similar to the sensitivity list. Whenever an event occurs on a signal to which the process is sensitive, the process is resumed. Figure 3.5 shows the example of a process that is controlled explicitly by the wait statement. In this example, the process statement contains one signal assignment statement and is followed by the wait statement. The signal assignment statement specifies that the signal output will obtain the result of 'or' of the values of the signal in1

```

Or_Process:

process(in1,in2)

begin

output <= in1 or in2;

end process;

```

Figure 3.4: Process Statement with Sensitivity List.

and in 2. The wait statement suspends the process until there is an event on either of the signals in 1 or in 2, at which time execution resumes at the top of the process statement.

In summary, a process is always active but the statements within a process are executed in sequence, one after the other. Although processes have parallel with hardware, and provide a natural way of modeling it, they are not best suitable for purpose of defining AHPL statement actions. In AHPL, all register transfer and bus connections are performed concurrently in a single step whereas in the process all statement are done sequentially. A better VHDL construct is the block statement that is described in the next section.

#### 3.2.3 Blocks

Similar to many programming languages VHDL provides a partitioning mechanism that allows the designer to logically group areas of the model. A block statement starting with keyword block and ending with keyword end, are used to group part of a design. A block can only be used within the architecture in which it has been designed and the statements within the block are executed concurrently.

Block structures are self-contained regions and each block may have a declarative part, which comes between the keywords block and begin. The declarative part may declare local signals, types, constants, etc. It may also define the interface to the block by using the port interface list.

```

Or_Process:

process

begin

output <= in1 or in2;

wait on in1, in2;

end process;

```

Figure 3.5: Process Statement with Wait Statement.

Block statements have an interesting feature known as guarded blocks. Guards in VHDL provide a facility to control the operation of signal assignment statement within the block. These signal assignment statements are known as guarded signal assignment and are recognized by the keyword guarded between the <= and the expression part of the statement.

A guarded block contains a guard expression after the keyword block. When the guard expression is true, all of the guarded signal assignment statements are enabled, or turned on. When the guard expression is false, all of the guarded signal assignment are disabled, or turned off. Whenever, a block has a guard expression, the VHDL compiler also implicitly defines a signal variable with the name guard, which can be used inside the block to trigger other processes to occur. This signal is read only and cannot be updated. Figure 3.6 illustrates the latch model of a D\_flipflop using the guarded block. There are two guarded signal assignment statements in this model. One is the statement that assigns a value to q, and the other is the statement that assigns a value to qb. When the clk signal has a value '1', the guard expression will be true, and the two guarded signal assignment statements are concurrently executed after their respective delay.

In summary blocks are very useful for partitioning the design into smaller and more manageable units. They allow the designer the flexibility to create large designs from smaller building blocks and provide a convenient method of controlling the execution of signal assignment statement. Based on this fact the VHDL block

```

d_flipflop: block(clk='1')

begin

q <= guarded d after delay1

qb <= guarded not(d) after delay2

end block d_flipflop;</pre>

```

Figure 3.6: Model of D\_flipflop Using Guarded Block.

AHPL step statement especially as each statement is executed concurrently within the block. Each transfer action can be translated as guarded signal assignment statement and the implicit guard is used to control the operation of signal assignment statement. The modeling of the AHPL register transfers and bus connections are described later in this chapter.

#### 3.2.4 State Machine

To model the finite state machine of the digital system, a mechanism that represents the state of the system is required. The current state of the control sequencer is represented by a binary vector of size equal to the number of steps in the AHPL module is used. In sequential systems all but one bit of this vector are low. However, for a parallel machine, depending on the number of concurrent activities (states), more than one bit may be high. The index of the high bit identifies the current state of the machine.

### 3.2.5 Modeling Trailing Edge Transfers

VHDL provides several options to model negative edge triggering. If the state is modeled as a process, one possibility is to use a wait statement at the beginning of the process. The statement wait until (clk='0') when included at the beginning of the process ensures that the process is executed only when the clock changes, and

that the change is from '1' to '0', representing the trailing edge. VHDL does not allow simultaneous use of a sensitivity list and wait statements. The reason is because that might create a contradiction within a process at execution time. Therefore we cannot put the clock signal in the sensitivity list of the process and have a wait on clock statement inside the process. Modeling a state as a process is not feasible since a state generally has more than one data transfer, which must be executed in parallel. The correct representation in VHDL of these concurrent transfers is via the block construct. To make the execution of the transfers within the block happen at the trailing edge, it is sufficient to make the block guarded on a trailing edge condition. This is the solution adopted in this work. Figure 3.7 shows how trailing edge condition can be implemented in VHDL.

As mentioned in the last section, the guard will control execution of all the statements within the block. The guard condition clock='0' and not clock'stable assures that all the guarded assignment statements will be executed immediately when the clock changes its state from '1' to '0' i.e., the trailing edge condition. The attribute property stable is used to ensure that the clock value is stable for the guard to become true.

### 3.2.6 Modeling Transfers to Buses

Since transfers to buses in a state are also executed in parallel, the model is similar to the one above, except that the trailing edge condition is removed from the guard

```

trailing_edge: block(clock='0' and not clock'stable)

begin

...

...

end block trailing_edge.;

```

Figure 3.7: Trailing Edge Implementation.

of the block. This method allows the bus connection to be made any time during the clock high edge, (i.e., when that particular state is active).

### 3.2.7 Modeling Conditional Transfers

In AHPL, there are three possible forms of a clocked transfer and two forms of a connection statement. In a simplest clocked transfer there is only one single source which is merely transferred into the destination register. The remaining two form conditional transfers, namely source control and destination control. Similarly, bus connection is either of simple connection or source control.

The source control can be easily implemented by appending a series of when and else clause at the end of the signal assignment statement for each of multiple sources. For each of the possible sources, its condition could be appended at the end of its when clause. The transfer or the connection will only be executed when its conditional statement is true. On the other hand, the destination control is best implemented by use of the if structure. The if statement is used to select destination signal to be updated based on the truth of the condition. Unfortunately, the if is not appropriate as the implementation of the composition process uses block structure to represent actions part for each state and the if is a sequential statement whilst the block structure only allow concurrent statements. However, block structure does allow the use of process statement which could include the if statement. The use of process and if statement is awkward method to implement destination control. A

better solution is to create a nested *block* with its guard used to condition for the destination control condition.

# 3.3 Mapping Summary

In this chapter a detail study of VHDL features was conducted and proposal was presented on how declarations, state automaton, edge triggered transfers, and other processes in AHPL can be mapped to VHDL. Modeling styles for the trailing edge and, the register transfer and bus connection were proposed using a subset of VHDL constructs. Ideally the *process* construct seems sufficient to model AHPL features but as revealed it is not the most suitable. The VHDL guarded blocks provide a very convenient method to model various aspect of AHPL specification.

Table 3.2 summarizes some of the important basic AHPL elements and features and their possible counter-parts.

| AHPL                     | VIIDI                                |  |  |

|--------------------------|--------------------------------------|--|--|

|                          | VHDL                                 |  |  |

| AHPL Module              | entity                               |  |  |

| CLUs                     | components                           |  |  |

| MEMORY                   | signals in the architecture body     |  |  |

| BUSES                    | signals in the architecture body     |  |  |

| INPUT lines              | port in entity declaration           |  |  |

| OUTPUT lines             | port in entity declaration           |  |  |

| Concept of state         | variable bit_vector                  |  |  |

| Trailing edge transition | process with 'wait until(clock='0')' |  |  |

|                          | or Guarded blocks with trailing edge |  |  |

|                          | condition included in the guard      |  |  |

| Connections to BUSES     | block of statements without guard of |  |  |

|                          | edge condition                       |  |  |

| Transfer to Registers    | block of statements with guard of    |  |  |

|                          | edge condition                       |  |  |

| State Transitions        | process with wait or guarded block   |  |  |

| ',' (catenation)         | &                                    |  |  |

| Reduction operator       | VHDL predefined function             |  |  |

| Source Control           | Nested when or else clause           |  |  |

| Destination Control      | Nested block structure               |  |  |

Table 3.2: Basic AHPL Modeling Elements/Features and their VHDL Counterparts.

# Chapter 4

# The Composition Process

In the last chapter, VHDL language was examined and a translation approach was defined. Based on the translation approach a mapping scheme from AHPL description to VHDL was derived using a subset of VHDL constructs. In this chapter, the mapping concept defined in the last chapter are utilized in the development of the composition process that allows the translation of the AHPL specification to its functionally equivalent VHDL model. Along with the overview of the composition process a detail description is also given for all its components.

The chapter ends with an illustrative example demonstrating the composition process. During the discussion of the components of the composition process, parts of an example were used to show the intermediatory results that are generated before the final VHDL model is produced.

## 4.1 Composition Overview

In this section a general overview is presented of the proposed composition process.

A brief overview is also given for the different components of the composition process and these components are discussed in more detail in the later sections.

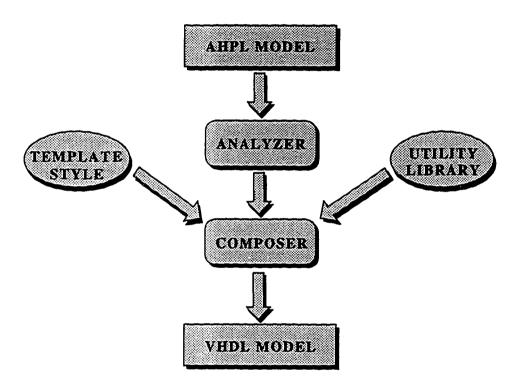

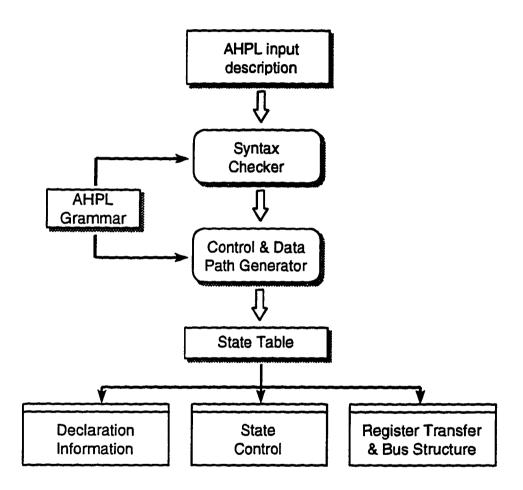

The composition process is a method of composing the AHPL specification and generating its corresponding functionally equivalent VHDL model. It is performed in two stages using several pre-defined composition tools. The block diagram of the composition process is given in Figure 4.1.

In the first stage, the Analyzer performs the syntax check for the input AHPL specification and produce intermediatory output for the Composer. Initially, the design specification written in AHPL is analyzed to check for syntactic errors. The Analyzer scans the AHPL code line by line and reports of any syntax format that is not allowed. Although the AHPL code may pass the syntactic correctness but there may still remain some semantic errors which are not detected by the Analyzer. It is left up to the user to make sure that no semantic faults exist in the input AHPL code.

If the description is syntactically correct, the Analyzer produces the required data structures of the data and control paths of the design. The generated data structures undergo a series of transformations to produce a concise tabular data structure capturing both the data and control (finite state machine) paths.

Figure 4.1: The Composition Process Steps.

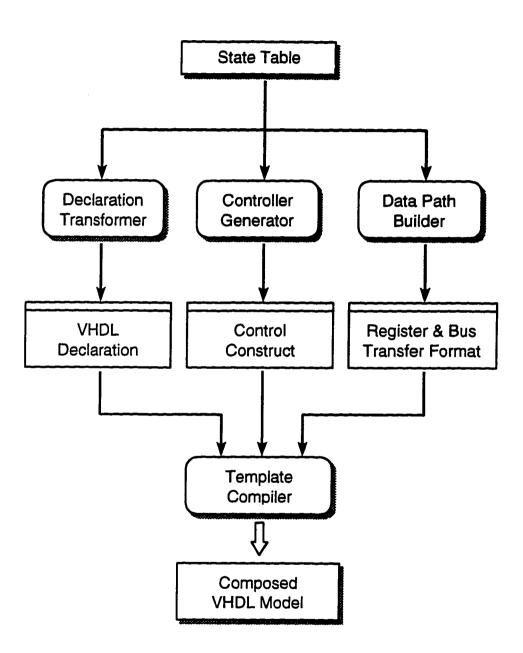

In the second stage the Composer utilizes the output of the Analyzer with the especially designed composition tools to generate the required VHDL output model [LG89]. There are two composition tools, The VHDL Template and The Utility Library, that were especially developed in order to simplify the composition process. The template structure is described later in this chapter. The Utility Library being used by the Composer contains predefined utilities that assist in the translation of many AHPL feature and functions.

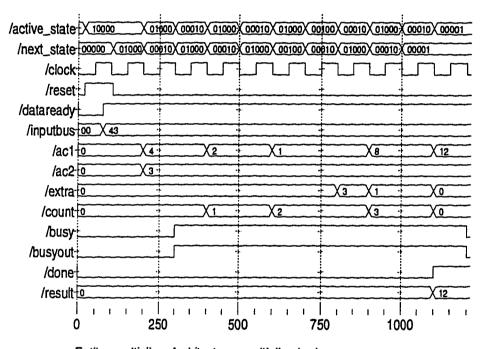

In the next few sections the components of the composition process are described in more details. The chapter concludes with an example of generated VHDL model for 4-bit Multiplier example of Figure 2.2.

## 4.2 The Analyzer

The primary role of the Analyzer is to diagnose and analyze the AHPL specification for the control and data path and accordingly generate FSM. It is also used to check for the syntactic correctness of AHPL code. Figure 4.2 shows the block diagram of the Analyzer.

The Analyzer performs its task in two steps. In the first step, the AHPL code is passed through the Syntactic Checker for the verification of the syntax. The AHPL input specification is fed in to the Syntax Checker and output is forwarded to Control & Data Path Generator. For Syntax Checker to perform for syntax correctness, the

Figure 4.2: The Analyzer Block Diagram.

AHPL grammar is also provided.

In the second step the FSM Control & Data Path Generator produces state tables. The Analyzer studies the declaration part, procedural part, and the non-procedural part of the AHPL description sequentially and generates comprehensive reports that fully describe the control actions of the AHPL specification. These reports are in the form of three tables:

- Declaration Information.

- State Control.

- Register Transfers & Bus Structures.

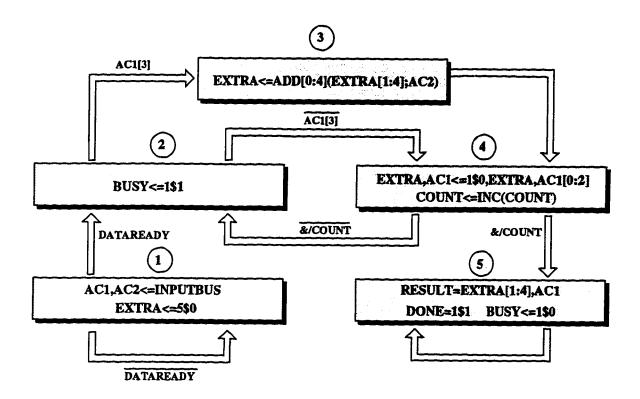

For the purpose of demonstration an extended-FSM is produced to show the information generated by the *Analyzer*. The FSM diagram for the AHPL description of Figure 2.2 is shown in Figure 4.3. The actual output produced by the *Analyzer* are three state tables as shown in Tables 4.1, 4.2 and 4.3.

### 4.2.1 The Analyzer Implementation

The Analyzer was built using classic UNIX compiler tools, namely lex and yacc [LMB92]. These tools were chosen as they provide powerful and flexible programming development environment to represent AHPL grammar. AHPL is a context-free grammar in Backus-Naur form and can be easily be encoded using the lex and

Figure 4.3: FSM Diagram of AHPL Model.

| name      | type         | length | source_cnt |  |

|-----------|--------------|--------|------------|--|

| acl       | memory       | 4      | 2          |  |

| ac2       | memory       | 4      | 1          |  |

| count     | memory       | 2      | 1          |  |

| extra     | memory       | 5      | 3          |  |

| busy      | memory       | 1      | 2          |  |

| dataready | exinput      | 1      | 0          |  |

| clock     | exinput      | 1      | 0          |  |

| reset     | exinput      | 1      | 0          |  |

| inputbus  | exbus        | 8      | 0          |  |

| result    | output       | 8      | 1          |  |

| done      | output       | 1      | 1          |  |

| busyout   | output       | 1      | 1          |  |

| inc       | clu=incr     | 2      | 0          |  |

| add       | dd clu=adder |        | 0          |  |

Table 4.1: Declaration Information Table.

| current_state | next_state | tran_cond          |

|---------------|------------|--------------------|

| 1             | 1          | dataready='0'      |

| 1             | 2          |                    |

| 2             | 4          | ac(3)='0'          |

| 2             | 3          |                    |

| 3             | 4          |                    |

| 4             | 2          | and_red(count)='0' |

| 4             | 5          |                    |

| 5             | 5          |                    |

Table 4.2: State Control Table.

| state | type     | dest_vect | dest_cond | sour_vect              | sour_cond |

|-------|----------|-----------|-----------|------------------------|-----------|

| 1     | register | acl       |           | inputbus(0 to 3)       |           |

| 1     | register | ac2       |           | inputbus(4 to 7)       |           |

| 1     | register | extra     |           | "00000"                |           |

| 2     | register | busy      |           | <b>'</b> 1'            |           |

| 3     | register | extra     |           | $add1\_out(0 to 4)$    |           |

| 4     | register | extra     |           | 0 & extra(0 to 3)      |           |

| 4     | register | acl       |           | extra(4) & acl(0 to 2) |           |

| 4     | register | count     |           | incl_out               |           |

| 5     | bus      | result    |           | extra(1 to 4) & ac1    |           |

| 5     | bus      | done      |           | <b>'</b> 1'            |           |

| 5     | register | busy      |           | <b>'</b> 0'            |           |

Table 4.3: Register & Bus Transfers Structure Table.

yacc tools. The yacc tool was used to generate the parser from the grammatical description of the AHPL language, while the lex tool was used for making lexical analyzer. The yacc tool in general provides a way to associate meanings with the components of the grammar in such a way that as the parsing takes place, the meaning can also be 'evaluated'.

The development of the Analyzer was performed in two steps. In the first step, the yacc tool was used for the specification of each rule or production of the AHPL grammar. For each rule, an action clause can be augmented - statement of what to do when an instance of that grammatical form is found in the AHPL code being parsed. This 'what to do' was written in C, with conventions for connecting the grammar to the C code. This part was used to define the semantic for the Control & Data Path Generator for purpose of extracting information for the state tables. In the second step, a lexical analyzer was created to read the input AHPL code being parsed and break it up into meaningful chunks for the parser. These lexical chunks are known as tokens and are used for defining of the keywords and symbols of the AHPL language. For each keyword and symbol of AHPL language recognized by the lexical analyzer a matching token was returned to the parser. There are two special types of tokens that are returned to parser: one for the string and one for the number. For both of these types the name corresponding to the token is return along with its value.

The complete lex and yacc programs for the Analyzer could be found in the

appendices. Figures 4.4 and 4.5 show a part of lex code and yacc production rule respectively. As can be seen in Figure 4.5, a yacc production rule comprises of two part. In the first part the definition of the grammar rule is stated and this is appended with an optional action part. The selected sample shows the production rule for the recognition of the 'module' head part of an AHPL code. The rule is looking for the keyword MODULE followed by the symbol ':' and an id string representing the name of the module. If this rule is satisfied, the action part of the production rule is executed and in this case it is simply printing the name of the module. For the yacc program to successfully match the different tokens, the lexical analyzer is intermediately invoked. For this particular production rule the three tokens are found by using the three lexical rules shown in Figure 4.4. The lexical rules are simply represented using the regular expression and if a match occurs its action part is executed. In all cases the name of the token is returned. For the tokens ID and CID its string value is also returned in the global variable id\_val and for token INTEGER its integer value is returned in the global variable int\_val.

### 4.2.2 State Table Generation

The lex and yacc tools used for the implementation of the Analyzer are initially used to perform the syntax check for each line of the AHPL code. The verified statements are then analyzed to extract all the information for the generation of the

Figure 4.4: Sample Lex Code.

```

modhead : MODULE COLON ID { printf("\nModule Name: %s\n",id_val); } ;

```

Figure 4.5: Sample Yacc Code.