**INFORMATION TO USERS**

This manuscript has been reproduced from the microfilm master. UMI

films the text directly from the original or copy submitted. Thus, some

thesis and dissertation copies are in typewriter face, while others may be

from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the

copy submitted. Broken or indistinct print, colored or poor quality

illustrations and photographs, print bleedthrough, substandard margins,

and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete

manuscript and there are missing pages, these will be noted. Also, if

unauthorized copyright material had to be removed, a note will indicate

the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by

sectioning the original, beginning at the upper left-hand corner and

continuing from left to right in equal sections with small overlaps. Each

original is also photographed in one exposure and is included in reduced

form at the back of the book.

Photographs included in the original manuscript have been reproduced

xerographically in this copy. Higher quality 6" x 9" black and white

photographic prints are available for any photographs or illustrations

appearing in this copy for an additional charge. Contact UMI directly to

order.

UMI

A Bell & Howell Information Company

300 North Zeeb Road, Ann Arbor MI 48106-1346 USA

313/761-4700 800/521-0600

# Optimization of Mixed CMOS/BiCMOS Circuits Using Tabu Search BY Mounir M. Zahra A Thesis Presented to the FACULTY OF THE COLLEGE OF GRADUATE STUDIES KING FAHD UNIVERSITY OF PETROLEUM & MINERALS DHAHRAN, SAUDI ARABIA In Partial Fulfillment of the Requirements for the Degree of MASTER OF SCIENCE In COMPUTER ENGINEERING July 1998

UMI Number: 1391850

UMI Microform 1391850 Copyright 1998, by UMI Company. All rights reserved.

This microform edition is protected against unauthorized copying under Title 17, United States Code.

300 North Zeeb Road Ann Arbor, MI 48103

# KING FAHD UNIVERSITY OF PETROLEUM AND MINERALS DHAHRAN, SAUDI ARABIA COLLEGE OF GRADUATE STUDIES

This thesis, written by

### MOUNIR MAHMOUD ZAHRA

under the direction of his Thesis Advisor and approved by his Thesis Committee, has been presented to and accepted by the Dean of the College of Graduate Studies, in partial fulfillment of the requirements for the degree of

### MASTER OF SCIENCE IN COMPUTER ENGINEERING

Thesis Committee

7, 71

Dr. Sadiq M.Sait (Chairman

r. Habio Youssef (Co - Chairman

Dr. Mostafa Abd - El - Barr (Member)

4/6

Dr. Khalid M. Al – Tawil (Department Chairman)

Dr. Abdallah M. Al - Shehri

(Dean, College of Graduate Studies)

20/8/98 Date

Dedicated to

My Parents,

Wife, and Brothers

# Acknowledgments

In the name of Allah, Most Gracious, Most Merciful. Read in the name of thy Lord and Cherisher, Who created. Created man from a {leech-like} clot. Read and thy Lord is Most Bountiful. He Who taught {the use of} the pen. Taught man that which he knew not. Nay, but man doth transgress all bounds. In that he looketh upon himself as self-sufficient. Verily, to thy Lord is the return {of all}.

(The Holy Quran, Surah 96)

All praise to Almighty Allah, who bestowed on me strength and patience to accomplish my goals. The acknowledgment is due to the King Fahd University of Petroleum & Minerals for providing me with tremendous support to this research work. I would like to express my indebtedness and sincere appreciation to Dr. Sadiq M. Sait, the chairman of the thesis committee, and Dr. Youssef Habib, co-chairman, who have been a constant source of guidance and encouragement throughout this work. I also appreciate the cooperation and support extended by Dr. Mostafa Abd Elbar who served as a committee member. I am thankful to all my friends and colleagues, whose kindness and understanding attitude made my stay, as a graduate student, a pleasant experience. Last but not the least, thanks are due to my parents, wife, and brothers for their prayers, guidance and moral support throughout my academic career.

# **Contents**

|   | Acl               | cnowledgments                            | iii  |  |  |  |  |  |  |  |

|---|-------------------|------------------------------------------|------|--|--|--|--|--|--|--|

|   | List of Figures   |                                          |      |  |  |  |  |  |  |  |

|   | List of Tables    |                                          |      |  |  |  |  |  |  |  |

|   | Abs               | stract (English)                         | ciii |  |  |  |  |  |  |  |

|   | Abstract (Arabic) |                                          |      |  |  |  |  |  |  |  |

| 1 | Inti              | oduction                                 | 1    |  |  |  |  |  |  |  |

|   | 1.1               | Importance of VLSI Circuits Optimization | 1    |  |  |  |  |  |  |  |

|   | 1.2               | Objectives and Scope of the Thesis       | 2    |  |  |  |  |  |  |  |

|   | 1.3               | Difficulties and Limitations             | 4    |  |  |  |  |  |  |  |

|   | 1.4               | Outline of the Thesis                    | 5    |  |  |  |  |  |  |  |

| 2 | Bac               | kground Material and Literature Review   | 7    |  |  |  |  |  |  |  |

|   | 2.1               | Introduction                             | 7    |  |  |  |  |  |  |  |

|   | 2.2 | VLSI Optimization                                 | 8          |

|---|-----|---------------------------------------------------|------------|

|   | 2.3 | Critical Path Problem                             | 11         |

|   |     | 2.3.1 Critical Path Algorithms                    | 14         |

|   | 2.4 | False Path Problem                                | 15         |

|   |     | 2.4.1 Sources of False Paths                      | 6          |

|   |     | 2.4.2 False Paths Detection Algorithms            | .7         |

|   | 2.5 | Optimization Techniques                           | <u>?</u> 1 |

|   | 2.6 | Summary                                           | <u> </u>   |

| 3 | Pro | blem Definition and Proposed Solution Technique 2 | E          |

|   |     |                                                   |            |

|   | 3.1 | Introduction                                      | 5          |

|   | 3.2 | Problem Definition                                | 6          |

|   |     | 3.2.1 Is COP in <i>NP</i> ?                       | 9          |

|   |     | 3.2.2 Is COP <i>NP</i> -Complete?                 | 1          |

|   | 3.3 | The Proposed Solution Technique                   | 3          |

|   |     | 3.3.1 Phase I                                     | 5          |

|   |     | 3.3.2 Phase II                                    | 6          |

|   |     | 3.3.3 Phase III                                   | 7          |

|   | 3.4 | Summary                                           | 8          |

| 1 | Tim | ing Analysis and False Path Problem 39            | 9          |

|   | 4 1 | Introduction                                      | Ω.         |

|   |     |                                                   |            |

|   | 4.2  | Timi   | ng Analysis and $\alpha$ -Critical Approach | 40 |

|---|------|--------|---------------------------------------------|----|

|   |      | 4.2.1  | Description of $\alpha$ -Critical Algorithm | 42 |

|   |      | 4.2.2  | Example                                     | 44 |

|   | 4.3  | False  | Path Problem                                | 44 |

|   |      | 4.3.1  | False Path Detection Algorithm              | 48 |

|   |      | 4.3.2  | Implementation Details                      | 58 |

|   | 4.4  | Exper  | rimental Results                            | 60 |

|   | 4.5  | Sumn   | nary                                        | 65 |

| 5 | Circ | cuit O | ptimization Problem Using Tabu Search       | 66 |

| _ |      |        | _                                           |    |

|   | 5.1  | Introd | luction                                     | 66 |

|   | 5.2  | Algori | ithm Description                            | 67 |

|   |      | 5.2.1  | Tabu Restriction                            | 68 |

|   |      | 5.2.2  | Aspiration Criteria                         | 70 |

|   |      | 5.2.3  | How the Algorithm Works                     | 70 |

|   | 5.3  | COP    | Formulation                                 | 72 |

|   |      | 5.3.1  | Initial, Current and Best Solution          | 72 |

|   |      | 5.3.2  | Generation of Moves                         | 75 |

|   |      | 5.3.3  | Tabu List                                   | 76 |

|   |      | 5.3.4  | Restriction Criteria                        | 77 |

|   |      | 5.3.5  | Aspiration Criteria                         | 77 |

|   |                                               | 5.3.6                                        | Evaluation Function                                                                                                                                                                                      | 78                            |

|---|-----------------------------------------------|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|

|   |                                               | 5.3.7                                        | Example                                                                                                                                                                                                  | 81                            |

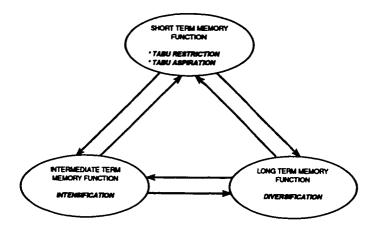

|   | 5.4                                           | Intern                                       | nediate and Long Term Memory                                                                                                                                                                             | 84                            |

|   |                                               | 5.4.1                                        | Intermediate Term Memory: Intensification Strategy                                                                                                                                                       | 84                            |

|   |                                               | 5.4.2                                        | Long Term Memory: Diversification Strategy                                                                                                                                                               | 88                            |

|   | 5.5                                           | Propo                                        | sed Frequency-based Diversification Strategy                                                                                                                                                             | 91                            |

|   | 5.6                                           | Evolu                                        | cionary Tabu Search                                                                                                                                                                                      | 92                            |

|   |                                               | 5.6.1                                        | Simulated Evolution Overview                                                                                                                                                                             | 93                            |

|   |                                               | 5.6.2                                        | Evolutionary Tabu Search                                                                                                                                                                                 | 95                            |

|   | 5.7                                           | Summ                                         | ary 9                                                                                                                                                                                                    | 98                            |

|   |                                               |                                              |                                                                                                                                                                                                          |                               |

| 6 | Imp                                           | olemen                                       | tation, Results and Discussion 10                                                                                                                                                                        | 0                             |

| 6 | <b>Imp</b> 6.1                                |                                              | tation, Results and Discussion 10                                                                                                                                                                        |                               |

| 6 |                                               | Introd                                       |                                                                                                                                                                                                          | 00                            |

| 6 | 6.1                                           | Introd                                       | uction                                                                                                                                                                                                   | 00                            |

| 6 | 6.1                                           | Introd<br>Impler                             | uction                                                                                                                                                                                                   | 00                            |

| 6 | 6.1                                           | Introd Impler 6.2.1                          | uction                                                                                                                                                                                                   | 00<br>01<br>01<br>5           |

| 6 | 6.1                                           | Introd Impler 6.2.1 6.2.2 6.2.3              | uction                                                                                                                                                                                                   | 00<br>01<br>01<br>05<br>8     |

| 6 | 6.1                                           | Introd Impler 6.2.1 6.2.2 6.2.3 Optim        | nentation Details                                                                                                                                                                                        | 000<br>01<br>01<br>05<br>8    |

| 6 | <ul><li>6.1</li><li>6.2</li><li>6.3</li></ul> | Introd Impler 6.2.1 6.2.2 6.2.3 Optim Experi | uction       10         nentation Details       10         Inputs/Outputs of the Program       10         Data Structures       10         Implementation Method       10         ization Tools       10 | 00<br>01<br>01<br>5<br>8<br>9 |

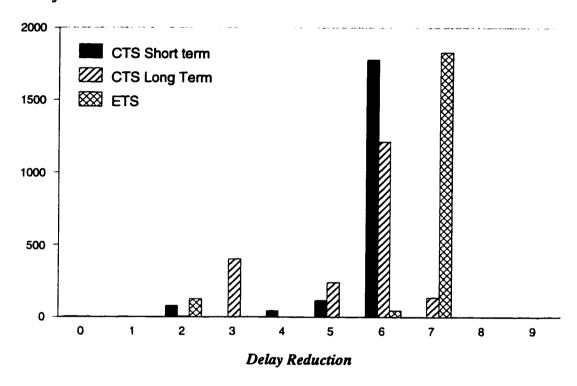

|   |      | 6.5.2  | Results of Short Term TS vs. Results of Long Term TS    | . 121 |

|---|------|--------|---------------------------------------------------------|-------|

|   |      | 6.5.3  | Results of TS with $AS_1$ vs. Results of TS with $AS_2$ | . 124 |

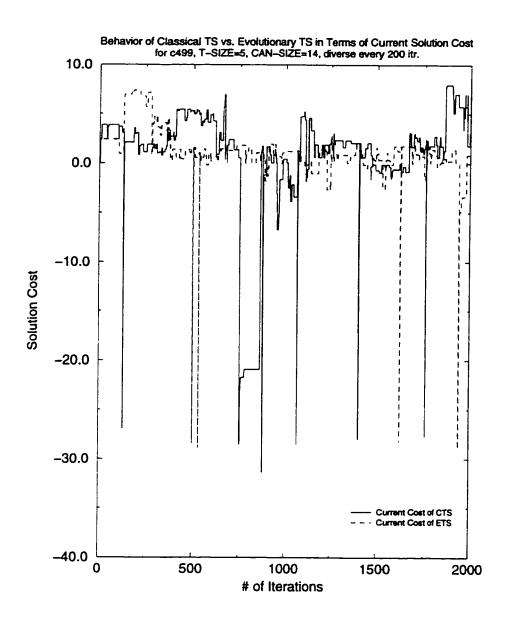

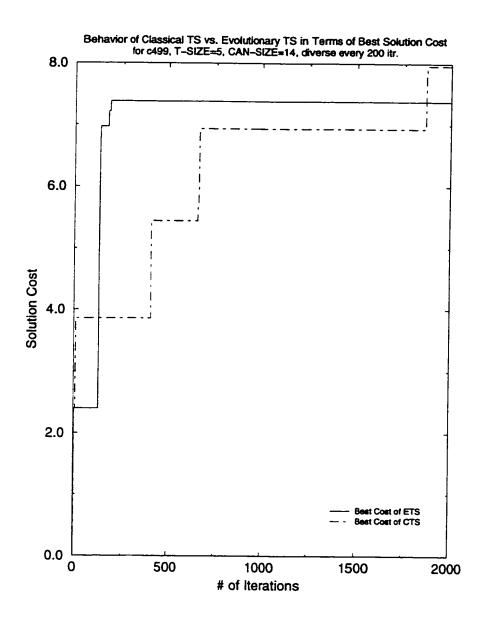

|   |      | 6.5.4  | Results of Classical TS vs. Results of Evolutionary TS  | . 126 |

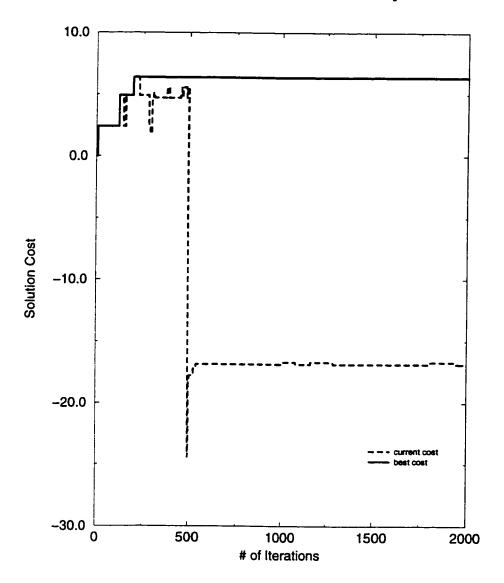

|   |      | 6.5.5  | Tabu Search Behavior                                    | . 130 |

|   | 6.6  | Summ   | nary                                                    | . 143 |

| 7 | Con  | clusio | n and Future Work                                       | 144   |

|   | 7.1  | Concl  | usion                                                   | . 144 |

|   | 7.2  | Future | e Work                                                  | . 147 |

|   |      | 7.2.1  | Other Mixed Technologies                                | . 147 |

|   |      | 7.2.2  | Selection of Critical Paths for Optimization            | . 148 |

|   |      | 7.2.3  | Some Tabu Search Issues                                 | . 149 |

|   | App  | endix  | A                                                       | 150   |

|   | Bibl | iograp | hy                                                      | 159   |

|   | Vita | L      |                                                         | 164   |

# List of Figures

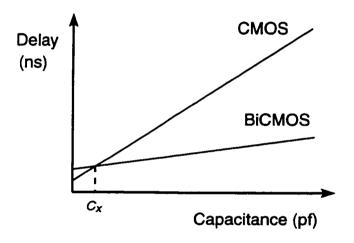

| 2.1 | Delay vs. load for CMOS and BiCMOS Nand gate                     | 12 |

|-----|------------------------------------------------------------------|----|

| 2.2 | Logic dependency is a source of false paths [PCM89]              | 18 |

| 3.1 | Nondeterministic COP algorithm                                   | 30 |

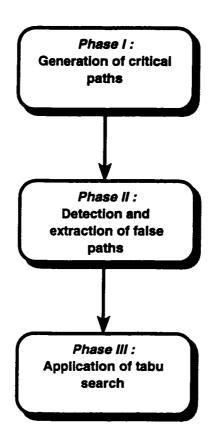

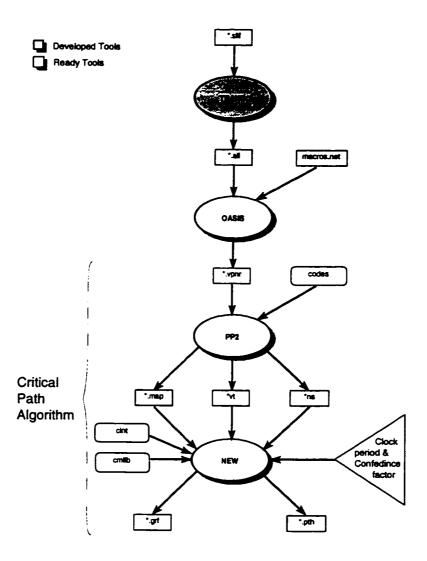

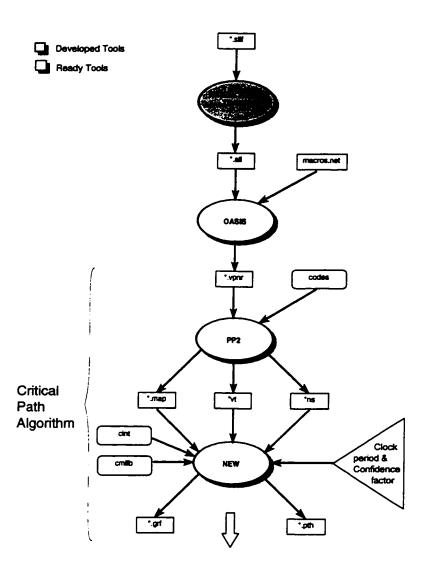

| 3.2 | General structure of the proposed solution technique             | 34 |

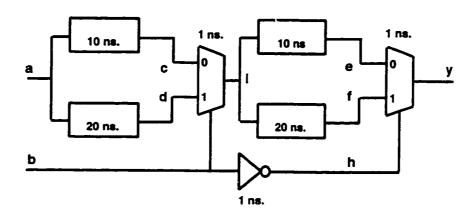

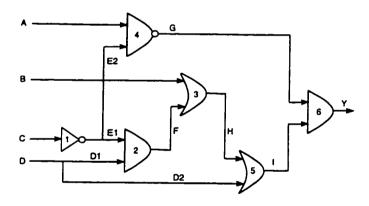

| 4.1 | A simple combinational circuit.                                  | 45 |

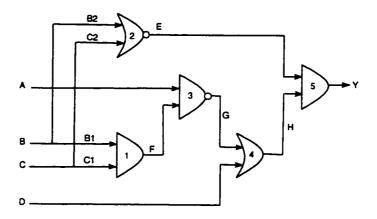

| 4.2 | Another simple combinational circuit                             | 47 |

| 4.3 | The false path detection algorithm (cont.)                       | 53 |

| 4.4 | The false path detection algorithm [DYG89]                       | 54 |

| 4.5 | Critical paths generation process for a circuit in SLIF format   | 62 |

| 5.1 | The relationship between memory functions of Tabu Search [Glo90] | 69 |

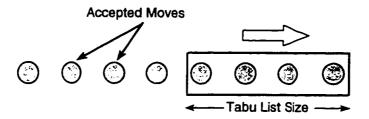

| 5.2 | Tabu list visualized as a window over accepted moves             | 71 |

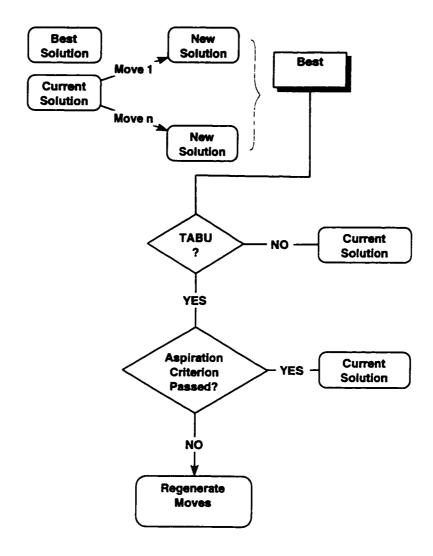

| 5.3 | Block diagram of tabu search procedure                           | 73 |

| 5.4 | Algorithmic description of Tabu Search (TS)                      | 74 |

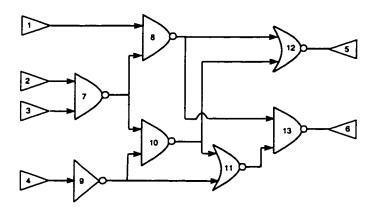

| 5.5 | A simple combinational circuit.                                  | 82 |

| 6.1  | Modified VPNR format of CKT                                             |

|------|-------------------------------------------------------------------------|

| 6.2  | Fanout description of CKT                                               |

| 6.3  | Sensitizable paths of CKT                                               |

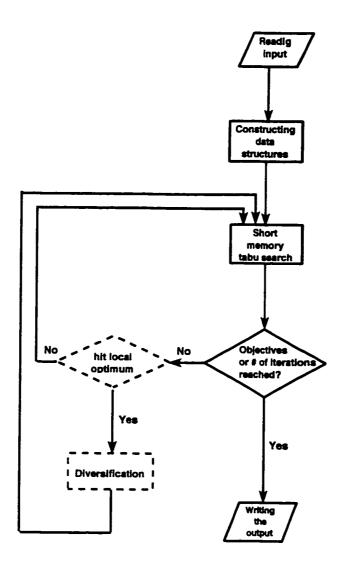

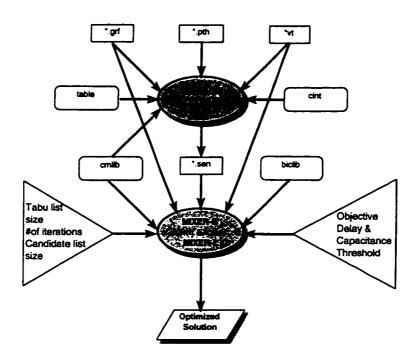

| 6.4  | The adopted TS based circuit optimization algorithm                     |

| 6.5  | Mixed CMOS/BiCMOS circuit optimization tools (cont.)                    |

| 6.6  | Mixed CMOS/BiCMOS circuit optimization tools                            |

| 6.7  | Effect of T_SIZE on delta delay for short term memory                   |

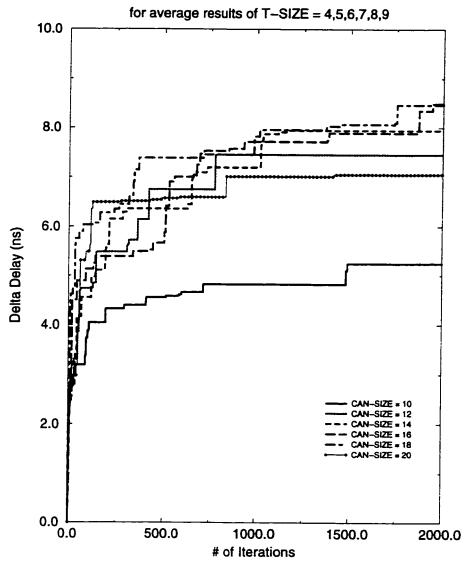

| 6.8  | Effect of CAN_SIZE on delta delay for short term memory 133             |

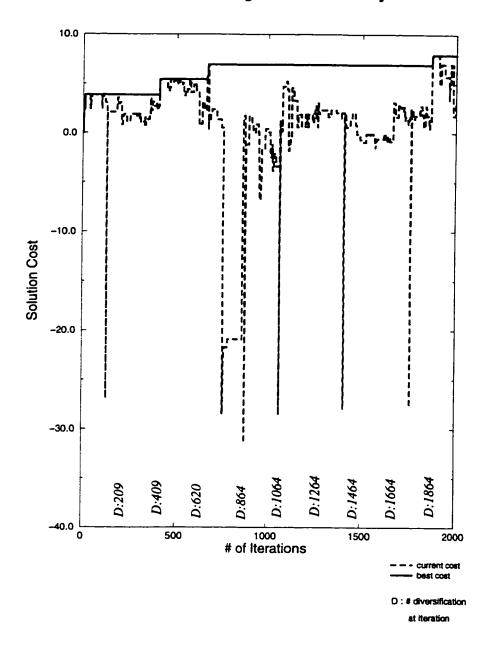

| 6.9  | Behavior of short term memory TS in terms of current and best cost. 135 |

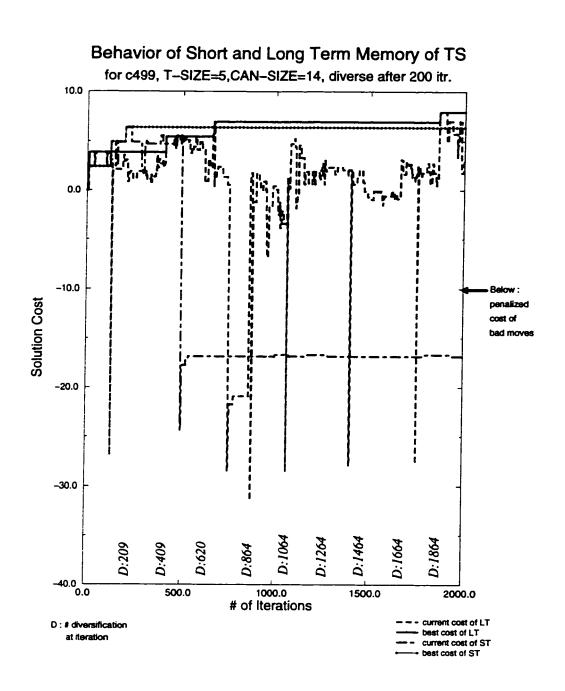

| 6.10 | Behavior of long term memory TS in terms of current and best cost 136   |

| 6.11 | Comparison between the behavior of short and long term memory TS. 137   |

| 6.12 | Comparison between the behavior of Classical TS and Evolutionary        |

|      | TS in terms of current solution cost                                    |

| 6.13 | Comparison between the behavior of Classical TS and Evolutionary        |

|      | TS in terms of best solution cost                                       |

| 6.14 | Solutions distribution 142                                              |

# List of Tables

| 4.1 | $Early\_arrive\_signals$ and $Late\_arrive\_signals$ of the path $P=C$ -    |

|-----|-----------------------------------------------------------------------------|

|     | 1 - E1 - 2 - F - 3 - H - 5 - I - 6 - Y                                      |

| 4.2 | Results of applying $\alpha$ -critical algorithm on some selected benchmark |

|     | circuits                                                                    |

| 4.3 | Some application results of the adopted false path detection algorithm. 64  |

| 5.1 | Iteration # 1                                                               |

| 5.2 | Iteration # 2                                                               |

| 6.1 | Sample of CMOS library                                                      |

| 6.2 | Circuit delay improvement results for some circuits                         |

| 6.3 | Best results of short term memory of TS with $AS_1$                         |

| 6.4 | Best results of long term memory of TS with $AS_1$                          |

| 6.5 | Best results of long term memory of TS with $AS_2$                          |

| 6.6 | Best results of long term memory of Evolutionary TS                         |

| 6.7 | Comparison    | between  | Classica. | ITS          | and | Evo | lutionary | 7 T | rs | in | ter | ms | of |     |

|-----|---------------|----------|-----------|--------------|-----|-----|-----------|-----|----|----|-----|----|----|-----|

|     | quality and p | performa | nce       | . <b>.</b> . |     |     |           |     |    |    |     |    |    | 129 |

### Abstract

Name: Mounir Zahra

Title: Optimization of Mixed CMOS/BiCMOS Circuits

Using Tabu Search

Major Field: Computer Engineering

Date of Degree: 1998

This thesis studies the problem of optimizing mixed CMOS/BiCMOS circuits using *Tabu Search* (TS) approach. Recently, many techniques have been proposed to improve the performance of VLSI circuits. Some of these techniques include: transistor sizing, buffer insertion, and optimal selection of different templates of the same technology.

For further improvement, a mixed technology design can be developed to take advantage of each technology. One possibility is to mix CMOS and BiCMOS cells within the same circuit in order to take advantage of the high speed and high driving capabilities of BiCMOS, and the regularity and low power consumption of CMOS.

The problem is formulated as a constrained combinatorial optimization problem. The proposed solution technique comprises three phases. In the first phase, critical paths of the input circuit are generated because circuit delay is determined by longest sensitizable paths only. Second phase involves the application of the false paths detection algorithm. Since some critical paths may be false, it is important to eliminate them in order to get the longest sensitizable paths. In the third phase, TS algorithm is applied on the longest sensitizable paths. This is the core phase of the proposed approach where TS is used as a heuristic technique for optimal selection of gates that need to be implemented in BiCMOS to maximize the circuit performance with minimum increase in power consumption and area.

As a part of the third phase, two new strategies have been proposed. First, frequency-based diversification strategy has been developed to be used in long term memory of TS. Second, we applied some concepts of *Simulated Evolution* algorithm in generating neighbor solutions to the current solution.

The achievement of the proposed technique is of two parts. First, it has been shown that TS is very effective and efficient in producing very good solutions to circuit optimization problem. Second, remarkable increase in speed (%10 - 30%) with negligible increase in the power and area (less than 5%) of mixed CMOS/BiCMOS circuits has been accomplished.

Although the technique has been applied to BiCMOS and CMOS technologies, it is generally applicable to other technologies as long as it is feasible and practical to mix them in one circuit.

### خلاصة الرسالة

الاسمالية منير محمود زخرا.

عنوان الرسالة : الوصول إلى المثالية ندو الر أشباه الموصلات المنتامة المؤكسة و الثنائية (سيموس، بايسيموس) باستخدام بحث "تابو"

مجال التخصص: هندسة حاسب ألى .

تاريخ الرسالية : يوليو ١٩٩٨ م.

في الأونة الأخيرة تم اقتراح العديد من الأساليب التقنية لتحسين أداء الدوائر المدمجة الضخمة، ومن هذه الأساليب:

- ١- التحكم بحجم التر انزيستور.

- ٢- استخدام الحو اجز بين الدو انر أو البو ابات.

- ٣- الاختيار الأمثل لوحدات بناء مختلفة من نفس نوع التقنية.

وللحصول على دو انر أكثر أداء ، من الممكن تصميم دو انر مدمجة من عدة تقنيات ، وذلك للاستفادة من ميز ات كل منها. ومن ذلك دمج تقنية سيموس وتقنية بايسيموس في دانرة و احدة للاستفادة من ميز ات السرعة العالية و القدرة على التحريك لدى تقنية بايسيموس، وميز ات استهلاك الطاقة المنخفض و النتاسق لدى تقنية سيموس.

تم في هذه الرسالة صياغة هذه المشكلة كاحدى مشاكل الوصول إلى المثالية في ترتيب ومعالجة عناصر حسابية في مجموعات بشكل مقيد. وتم اقتراح أسلوب تقني فعال لتطوير وتحسين أداء دوانر مدمجة من تقنية سيموس، بايسيموس بأقل زيادة ممكنة في المساحة والطاقة المستهلكة، ويتكون الأسلوب المقترح من ثلاث مراحل. المرحلة الأولى والثانية تتضمن توليد أطول الطرق الصحيحة التي تحدد سرعة الدائرة حيث يتم توليد الطرق الحرجة أو لا ثم تطبيق خوارزمية الكثيف عن الطرق الخاطنة لعزلها من الطرق الحرجة. وتتضمن المرحلة الثالثة تطبيق طريقة "تابو" لإيجاد أطول الطرق الصحيحة، وتمثل المرحلة الرنيسية في عملية التحسين كلها، حيث يتم استخدام طريقة "تابو" للبحث كأسلوب تتقيبي في عملية الاختيار الأمثل لبعض البوابات التي يمكن تنفيذها من تقنية بايسيموس، وذلك لزيادة سرعة الدائرة بأقل ما يمكن من الطاقة المستهلكة و المساحة. وكجزء من هذه المرحلة تم اقتراح و استخدام طريقتين جديدتين : الأولى في عملية توسيع مجال البحث المستخدمة في الذاكرة الطويلة المدى من طريقة "تابو" والثانية في تطبيق بعض مفاهيم خوارزمية "التقدم المحاكى" في عملية توليد الحلول المجاورة للحل الحالى .

باستخدام وتصبيق هذا الاسلوب تم تحقيق انجازين هامين:

١- بيان فعالية أسلوب "تابو" في ايجاد الحلول الجيدة و المطلوبة لمشكلة الوصول إلى المثالية للدو الر المدمجة.

٢- الحصول على زيادة عالية في سرعة الدواسر المدمجة (حوالي ١٠٥% -٣٥٠٠) بزيادة طفيفة في المساحة والطاقة المستهلكة (اقل من ٥٥٥٥).

وكما تد تطبيق هذا الدمج على تقنية سيموس وبالسبموس فيمكن تعميمه على تقنيات أخرى مع الأخذ بالاعتبار ملائمة وامكانية دمجها عمليا

# Chapter 1

# Introduction

# 1.1 Importance of VLSI Circuits Optimization

Nowadays, CMOS technology has qualified to be the most appropriate choice in VLSI applications because of its low DC power dissipation and its high package density. However, the demand for superior performance, which has motivated the research and development of new technology, was behind the emergence of BiCMOS technology. BiCMOS is a combination of CMOS and Bipolar technologies which take advantage of their qualities; namely high speed and high driving capabilities of Bipolar, and small area and low power consumption of CMOS. This kind of optimization is achieved in the logic level resulting in an optimization of the entire network [EBE93].

Many techniques have been proposed to improve the performance of VLSI circuits

at the physical level. One of these techniques is to optimize the logic blocks that constitute these circuits. In the standard cells design, the optimization can be made by an optimal selection of functional cells from a cell library. This type of library is composed of different versions of cells of different characteristics such as size and delay. However all the cells use the same technology (e.g., CMOS) [LMSK90].

For further improvement of the performance of VLSI circuits, a mixed technology design can be developed to take advantage of the individual technology. One possibility is to mix CMOS and BiCMOS cells within the same circuit in order utilize the high speed and high driving capabilities of BiCMOS, and the regularity and low power consumption of CMOS.

# 1.2 Objectives and Scope of the Thesis

The objective of the thesis is to develop a methodology and right tools to optimize mixed CMOS/BiCMOS circuits in terms of delay, power and area. Although the scope of the work is directed to CMOS and BiCMOS technologies, other technologies can be included taking into consideration the feasibility and practicality of mixing these technologies. The input circuits are in standard cell format. The basic idea is as follows. Given a circuit consisting of CMOS cells only, some of those cells are selected and replaced by their equivalent BiCMOS cells in such a way that the entire delay of the circuit is decreased with a minimum increase in power and area.

Several questions can be raised while achieving this objective: What are the cells that have to be selected? Do we have to consider all the cells in this process? Is the selection problem NP-hard? What is the most efficient method for selection to produce the objective optimized circuit? How are the delay and power of a given circuit calculated? These questions and others are answered in this thesis. For ease of reference, we will refer to the problem of cells selection for optimizing a given circuit as Circuit Optimization Problem (COP).

Although the idea of our work is based on the work done in [BAB94], the approach and methodology are different. The proposed approach is more efficient and faster because the search space is restricted to a portion of the circuit rather than the entire circuit. The results are better and more accurate than those found in [BAB94].

We focused on delay and power for optimization. Area of layout is not considered because it is not affected much in the process as the difference in area between CMOS and BiCMOS cells is slight compared to other technologies. When other technologies of large area scale are meant for this type of optimization, our method has to be slightly modified to incorporate the area factor.

### 1.3 Difficulties and Limitations

Given below is a summary of difficulties and limitations encountered as normal in a research work.

- Lack of resources related to this field of research, particularly in the BiCMOS technology.

- 2. Development and usage of the tools have been done on different platforms, hence the tools have to be modified slightly each time the platform is changed.

- 3. Non-availability of BiCMOS cell library.

- 4. Non-availability of power model for BiCMOS technology in the literature. In order to overcome this problem, capacitance is used as proportional to the power. This point will be explained later.

- 5. Limitation of the tools that have been used for generating critical paths of a given circuit. The tools work only for small circuits and do not consider the elimination of false paths.

- 6. Difficulties in obtaining benchmark circuits in VPNR format which is the input to critical paths tools. For this issue, different tools have been used to convert the available ISCAS'85 benchmark circuits into VPNR format.

### 1.4 Outline of the Thesis

This thesis describes in detail the work that has been done to address COP. It covers all the research, processes, algorithms, tools, methodologies, implementation, results, analysis and discussions. Throughout the thesis, each chapter begins with an introduction that serves as a link to the preceding one and gives an overview of that chapter. Also, each chapter concludes with a summary of the main ideas and outcomes. Whenever essential, the ideas and points in reference are followed by a figure or an illustration. The thesis is organized as follows. Chapter 2 presents material background and literature review on most of related research previously made. In Chapter 3, the idea of our work is explained and formal definition of COP is presented. Also the proposed solution process and technique that have been adopted are provided in this chapter. The proposed solution consists of three phases. The details of phase I and phase II are presented in Chapter 4 while details of phase III are presented in Chapter 5. Chapter 4 highlights the timing analysis and critical path problem and gives a detailed description of the algorithm used in our work. In addition, this chapter discusses the problem of false paths as well as the adopted false path detection algorithm supported with an illustrative example. Chapter 5 deals with Tabu Search technique which is the main part of the proposed solution approach to COP. Explanation of tabu search and all its memory components is presented. In addition, in this chapter, we explained the process of modeling COP

to fit with tabu search technique. Methods of implementing and applying TS on COP, experiments, results, and discussions are provided in Chapter 6. Finally, our conclusions and future work are discussed in Chapter 7.

Appendix A provides a detailed information on the adopted tools such as execution procedure, format of input circuits, and limitations of the tools. In addition, it provides the CMOS and BiCMOS libraries and other tables used in this work.

# Chapter 2

# Background Material and

# Literature Review

### 2.1 Introduction

This chapter provides background about some materials, ideas, methodologies, and processes related to the work. It is an important introduction to the subsequent chapters which discuss COP and the proposed approach for its solution. In Section 2 of this chapter, an overview regarding optimization of VLSI circuits is presented with emphasis on the earlier works in this field. Section 3 addresses critical path and false path problems and reviews some well known algorithms proposed to solve such problems. The last section deals with some of the recent techniques developed for solving common optimization problems such as quadratic assignment and graph

coloring.

# 2.2 VLSI Optimization

A combinational circuit is required to operate as fast as possible and in no case slower than a given speed limit. That is, the delay of a circuit should not be longer than the system clock period. If a circuit is verified to be slower than the clock period, its performance needs to be improved. However, most of the time the improvement in performance is achieved at the expense of extra area and extra power. Therefore, many techniques have been proposed to optimize circuits in terms of those three parameters, especially in VLSI circuits where area and power are important issues.

According to the design level, optimization techniques can be divided into three categories:

- 1. At the structural level, the internal structure of gates and their interconnections are modified to improve circuit performance. For example, the technique of converting a ripple-carry adder into carry-lookahead adder by the use of Shannon factorization belongs to this category [CDL93].

- 2. At the **physical level**, performance-driven placement of gates and performance-driven routing of wires are aimed at minimizing the delay of the longest paths [CDL93].

3. At the gate/circuit level, techniques for transistor sizing, buffering and powering are used to improve gate speed while the topology of the whole circuit is retained [CDL93].

Due to their ability of retaining circuit topology, gate/circuit level optimization techniques are usually the first to be employed in optimization process. Physical or structural level techniques are applied when gate/circuit techniques cannot achieve the goal [CDL93].

One of the main techniques applied at the gate/circuit level, is the optimization of logic blocks constituting the VLSI circuits in terms of speed and area. When using standard cells approach, the optimization can be performed by an optimal selection of different templates (gates or cells) in the same technology. These templates differ in area, driving capabilities, intrinsic delay, and capacitive loading [LMSK90].

For further improvement of performance of VLSI circuits with minimum area and power penalty, a mixed design of different technologies can be adopted. One possible choice is to mix CMOS and BiCMOS technologies in order to take advantage of their qualities, namely high speed and high driving capability of BiCMOS, and regularity and low power consumption of CMOS. In terms of manufacturing process, this mixture is feasible in the sense that the CMOS process is part of the BiCMOS process. The CMOS-based BiCMOS process is a CMOS baseline process to which a bipolar transistor is added [EBE93]. Therefore, for developing mixed design circuits, initially all cells are exposed to CMOS process. Then bipolar transistors

will be added only to those cells that are selected to be BiCMOS.

In [BAB94], the above approach for optimizing standard cells circuits has been used. The technique aims at improving circuit performance by making for each gate, a choice between CMOS or BiCMOS cells depending on their load capacitance. The comparison between CMOS and BiCMOS gate delay driving a capacitive load CL shows that the two curves intersect at the crosspoint CX as shown in Figure 2.1. Based on this feature, the selection technique is applied as follows:

- 1. Initially, all gates are considered as CMOS in order to increase circuit density.

- 2. Output gates are replaced by BiCMOS gates because the inter-block wiring capacitance is assumed to be large.

- 3. The remaining gates are selected by comparing the value of their respective output load capacitance to the corresponding crossover capacitance CX. This load is equal to the sum of all input capacitance of the driven gates and the interconnection load.

- 4. Since all gates driven by the gate under check must have already been selected, a Breadth First Search (BFS) is adopted. The BFS algorithm reported in [BAB94] successively selects gates according to their decreasing logical level, from the primary outputs to the primary inputs. The BFS algorithm associates with each gate a counter representing the number of driven gates. Each time a gate is selected, the counters of all gates driving it are decremented.

The algorithm has been tested on ISCAS'85 benchmark circuits and achieved speed improvement by about 11% to 41% as compared to their pure CMOS version. The overhead in terms of area and power is shown to be small [BAB94].

Although the reported approach achieved a good improvement in performance, it suffers from several problems as follows:

- 1. Traversing all the nodes is not a necessary step because it is time consuming.

- 2. Replacing all output nodes produces overhead in area and power because some of them are not on time critical paths.

- 3. This approach is local; that is, it performs the optimization on a single node. It does not have a global view of the circuit, hence it is expected to give a local optimum solution.

- 4. It is not oriented not path oriented; hence it does not show the actual delay of the circuit.

### 2.3 Critical Path Problem

The actual delay of a circuit is determined by the delay of its longest sensitizable path. A sensitizable path is the path which can be activated by at least one input vector. The paths which cannot be activated by any input vector are called false paths. A path is critical if its total delay is greater than the clock period. Thus, the

Figure 2.1: Delay vs. load for CMOS and BiCMOS Nand gate.

path problem [CDL93]. Only the sensitizable paths are called "critical paths" by some authors. In this work, the term "critical paths" refers to both sensitizable and false paths.

Timing simulation and timing analysis are two popular approaches to verify the delay characteristics of combinational circuits. A timing simulation algorithm simulates each input vector on the circuit so as to identify all the sensitizable paths. After finding all the sensitizable paths, the simulation algorithm returns the delay of the longest paths as the actual delay of the circuit. Due to the very large computation time required to simulate all the vectors which grows exponentially with the complexity of the circuit, researchers focus more on the timing analysis approach.

Timing analysis ignores the logic properties of the circuit elements and checks only the timing behavior of the circuit. This fact makes timing analysis very time efficient as compared to simulation. Ignoring the functionality of the circuit elements, however, is responsible for the difficulty of the false path problem.

In most of timing analysis techniques, the circuit is modeled as acyclic directed graph in which three famous algorithms are used to trace the paths. These algorithm include Depth First Search (DFS) with/without pruning, Breadth First Search (BFS) and PERT-like trace [AF95].

### 2.3.1 Critical Path Algorithms

One approach to critical path prediction is to report the most critical path in the circuit. This approach is also referred to as the *Block Oriented Approach* [YDG89]. However, reporting only the most critical path often fails to give sufficient information to the designer to correct the timing violations because there might be more than one longest path having the same delay or the subsequent longest paths may violate the timing constraints as well.

To get more information, another approach called *Path Enumeration* is taken up in which all the paths are enumerated and then critical paths violating some timing constraints are reported. Although this approach gives more information than the previous one, it suffers from the large computation due to the fact that the total number of paths grows exponentially with the size of the design [YDG89].

A third approach is to find the K most critical paths. In this approach, all the paths which are greater or smaller than a given threshold are reported. The threshold is usually the clock period but it can be of any timing limit. A variation of this approach is reported in [YDG89]. In this algorithm, if the given threshold is too small, the number of paths being reported will increase rapidly. Therefore, it is preferable to choose a proper threshold and limit the number of paths to the K most paths [YDG89].

The algorithm reported in [You90] also provides the K most critical paths in

descending order. In this algorithm, a score is computed for each enumerated path. The score is a function of parameters that are correlated with the total path delay. Examples of these parameters include: load factors, number of nets on the path, etc. The K paths with worst scores are the K most critical paths. Linear regression model is used to predict the delay of interconnections at the net level as well as at the path level. However, the regression approach does not produce desirable results due to the large prediction errors of the model.

A variation of the above approach has been proposed in [AF95]. This approach is called  $\alpha$ -critical and described in detail in Chapter 4. The time complexity of these algorithms is proportional to the reported number of critical paths [AF95].

### 2.4 False Path Problem

The timing analysis based techniques ignores the functionality of the circuit. These techniques aim at finding the longest paths either sensitizable (true) or unsensitizable (false). The presence of false paths has many undesirable effects:

- The loss of accuracy. There is no theoretical limit between the longest true

path and the longest false path. Therefore the loss of accuracy can be large

and results in loss of confidence in the timing analysis tool.

- Waste of optimization effort. Since the longest propagation path determines the length of the clock period, a large difference between the longest false path

and the longest true path will result in unnecessary conservative designs, or alternatively wasted power and silicon area. Thus, eventually optimization efforts will be spent on false paths rather than on the true paths.

### 2.4.1 Sources of False Paths

- Incompatible transitions: In this very simple case, a false path results from the combination of incompatible transition. For example, in subsequent inverters, the addition of the delays associated with the 1 → 0 transitions instead of alternating the 1 → 0 and 0 → 1 transitions [BMCM90] is a source of false paths.

- 2. Incorrect signal flow: Timing verifiers that operate at switch level encounter this problem. Due to the bi-directional nature of MOS transistors, the intended signal flow in structures such as barrel shifter is not always obvious [BMCM90].

- 3. Synchronization: Whether the synchronization is simply performed within the clocking scheme or in a more complex way, it implies that signals are latched and have to wait for next synchronization point. When transparent latches are used, depending on their arrival time, signals might be allowed to continue to propagate. Therefore, the propagation conditions of these latches may or may not be compatible with those of the path that lead to them. In the latter case, ignoring these conditions will lead some timing verifiers to incorrectly

view these latches and subsequent combinational logic as part of the path [BMCM90].

4. Logic dependency: The most explicit source of false paths comes from some logic that depends on the output of other logic. For example, in the circuit shown in Figure 2.2, the path a d i f y can not be activated because both multiplexers can not select 1-input at the same time [PCM89].

### 2.4.2 False Paths Detection Algorithms

Recently a number of techniques have been proposed to detect the false paths. Some of them aim at finding the sensitizable paths directly, hence avoiding false paths reporting. Other techniques detect the false paths and remove them from reporting to the designer. Each of these techniques uses a path sensitization criterion. All of the reported criteria can be classified into three main conditions: *Static, Dynamic* and *Viable*. This section gives an overview regarding most of the false paths detection techniques according to these three conditions.

### Static Sensitization:

The first techniques to detect false paths are based on D-Algorithm which is used extensively in testing. One important assumption of the D-Algorithm is that, except the signal to be propagated, all other signals in the circuit are assumed to be always stable. A signal s becomes stable when it has the logical value determined by the

Figure 2.2: Logic dependency is a source of false paths [PCM89].

Boolean expression of s and the logical values of primary inputs. This assumption, however, is not applicable when the D-Algorithm is used for the detection of false paths because it will give incorrect results. First it will report some paths as false paths while in reality they are not. Second, it can underestimate the sensitizable path length. In Chapter 4, we will show one example that demonstrates these effects. Some of the algorithms that use static conditions are reported in [Rot66], [BI86], and [BMCM90].

#### Dynamic Sensitization:

Since the algorithms based on static sensitization generate inaccurate results as mentioned above, some researchers propose other techniques that release the assumption of the D-algorithm.

In [DYG89], the authors propose an algorithm to detect whether a given path is false or not by using an input independent approach which takes the *stable* time of signals into account. They show that the time required for a signal to be stable depends highly on both the stable times and logical values of its input signals. The detail of this algorithm will be presented in Chapter 4.

Another approach that computes the longest dynamically sensitizable paths has been proposed in [PCM89]. In this approach, propagation conditions for the signals that take the dynamic behavior of the circuit into account are used. The propagation condition for a certain signal explicitly depends upon arrival time of its predecessors.

Two approaches proposed in [HPS93] use what is called Timed Boolean Cal-

culus. The dynamic behavior of a given logic circuit is modeled as timed Boolean expressions. Then for each term in the expressions, its corresponding sensitizability function is computed. The terms whose sensitizability functions are not satisfiable are removed and the maximal delay for each node are determined from the remaining terms. For a given path, if the maximal delay of one of its internal node is greater than the maximal delay of any of the successor nodes, then that path is claimed to be false.

Chen and Du [CD93] have proposed three sensitization criteria; namely exact, loose, and dynamic. In exact criterion, all input vectors that can activate a given path are found. So, if no vectors are found, then the path is claimed to be false. This criterion is called exact because it can yield exactly the same critical path delay as the gate level timing simulation approach. Loose criterion is used to make the comparison between different criteria easier in the sense that some proposed criteria are meant for sensitization of long paths only, not for general path sensitization problem. Under dynamic criterion, a lead (signal on the path under test) is considered to dominate its succeeding gate if it is either a lowest earliest controlling input or a noncontrolling input with all its side inputs being noncontrolling inputs too. Using this criterion, at least one critical path is identified.

#### Viability:

The flaw in the dynamic sensitization condition is the absence of perfect knowledge of the delay of gates. In such case, both the exact value of any node at any time before the node has settled to a final value and the time at which a node settles to a final value is problematic. That means the above mentioned methods use criteria which are non-robust.

MaGeer and Brayton [MB89] developed a technique that computes the longest viable path in combinatorial circuits. Their technique is based on two conditions: correctness and robustness. These two requirements are derived from the idea of Boolean Difference. A path is defined to be sensitizable if there exists at least one input vector to allow a transition to propagate through the path. The path sensitization criterion associates the path with a Boolean expression, which represents the set of input vectors that activate the path. If the associated Boolean expression of the path is computed to equal logic 0, the path is claimed to be a false path.

# 2.5 Optimization Techniques

The problem of optimizing mixed technology design is considered as one of combinatorial problems. For a mixed CMOS/BiCMOS design, there exist  $2^n$  solutions for a circuit with n gates. Therefore, it can not be solved by polynomial-time algorithms. Heuristic techniques can be applied which generate optimal and near optimal solutions to a wide variety of NP-complete problems. Colin Reeves defines a heuristic as "a technique which seeks good (i.e., near-optimal) solutions at a reasonable computational cost without being able to generate either feasibility or optimality, or

even in many cases to state how close to optimality a particular feasible solution is" [Ree95].

Heuristic techniques can be classified into deterministic and nondeterministic. A deterministic algorithm progresses toward the solution by making deterministic decisions. On the other hand a non-deterministic algorithm makes random decision to find the solution. Therefore, deterministic algorithms always produce the same solution for a given input instance, while non-deterministic algorithms may produce different solutions. Another classification of heuristic algorithms is based on the initial input: Constructive and Iterative. A Constructive heuristic algorithm receives the problem description as input and then constructs a solution to the problem. An iterative heuristic algorithm receives the problem description and an initial solution as input. Then it attempts to modify the initial solution so as to improve a cost function. The iterative procedure is applied repeatedly until no cost improvement is possible. Usually, a constructive technique is first applied to find a certain solution and then an iterative technique is applied to produce a better solution.

Recently, several heuristic techniques have been proposed to find optimal and near optimal solutions to a wide variety of classical and practical optimization problems. Some of these well known techniques include Simulated Annealing, Genetic Algorithm and Tabu Search [SY95]. They have been applied in areas ranging from scheduling to telecommunications, and from character recognition to neural networks.

Simulated Annealing is an adaptive heuristic technique which was first introduced by Kirkpatrick, Gelatt and Vecchi in 1993. It was first used for trying to obtain a good crystal structure of a metal through a process of heating it to high temperature to break the chemical bond and then slowly cooling it to get a certain structure. By varying the cooling rate, time of the annealing process, and other parameters, we get different results.

Comparing the annealing process to optimization process, the aim of getting global optimum solution is analogous to the aim of getting a good crystal structure.

Genetic Algorithm derives its name from the natural process of evolution to get the optimum characteristics of an individual from a large population of different characteristics. The idea of this algorithm is as follows. Given a set of strings of symbols, during each iteration, the strings in the current solution are evaluated using some measures of *fitness*. Based on the fitness, two strings at a time are selected and a number of genetic operations are applied on the selected strings to generate a new string. These operations include *crossover*, *mutation* and *inversion*. The process is repeated until an optimum string is obtained [SY95].

Tabu Search is a *metaheuristic* which can be used as an independent search technique or as a higher level heuristic procedure for solving problems. It is basically designed to guide other methods to escape the trap of local optimality. TS operates by incorporating flexible memory functions to forbid transitions (*moves*) between solutions that reinstate certain attributes of past solutions. Attributes that are not

permitted to be reinstated are called *tabu*, and are maintained in short term memory on a list called *tabu list*. After a specified duration they are removed from the list and become free for re-insertion.

In a variety of problems, TS has found solutions superior to the best previously obtained by alternative methods. In other cases, it has demonstrated advantages in ease of implementation or in the ability to handle additional considerations such as constraints not encompassed by an original problem formulation [Glo90].

Some of the main applications of TS include: bandwidth packing [LG93a], quadratic assignment problem [BT94], graph coloring [Hd87], graph partitioning [LC91], VLSI placement [SV92], and scheduling and allocation in high-level synthesis [Ali94].

# 2.6 Summary

In this chapter, some background on VLSI optimization, critical and false paths problems, and some of the optimization techniques have been addressed. In addition, we have presented some proposed techniques very popular in each area. Our proposed approach to the COP, as will be shown later, is strongly based on these concepts and algorithms.

# Chapter 3

# Problem Definition and Proposed

# Solution Technique

### 3.1 Introduction

The COP is an NP-Complete problem. However, this claim needs to be proved based on the theories of NP-hard and NP-complete problems. In this chapter, a formal definition of the COP is given. Then we prove that this problem is NP-complete and therefore requires a heuristic technique for its solution. Finally, the proposed technique of generating an optimized mixed CMOS/BiCMOS circuit is presented.

### 3.2 Problem Definition

The objective of this work is to find an optimal or near-optimal solution to the problem of mixing CMOS/BiCMOS gates in one circuit such that the overall delay is minimized with minimum increase in the power and area. Only the longest sensitizable paths, that the delay of a circuit depends on, are considered in the search. Moreover, the BiCMOS gate has less delay than the corresponding CMOS only if its fanout load capacitance CL is greater than a certain threshold CX as mentioned in [BAB94]. Therefore only those nodes with CL > CX will be considered.

Given a circuit with m nodes and K sensitizable paths, we should first extract all nodes that are included in the sensitizable paths and satisfy the inequality CL > CX. Let A be the set of such nodes and let n be the size of this set.

The input for the COP is:

- Set  $A = (g_1, g_2, \ldots, g_n)$

- Vector  $\mathcal{D} = (\Delta D_1, \Delta D_2, \dots, \Delta D_n)$

$$\Delta D_i = D_{g_i}^c - D_{g_i}^b$$

where:

$\Delta D_i$  is the circuit delay gain due to changing gate i implementation from CMOS to BiCMOS. Obviously, for all  $g_i \in A$ ,  $\Delta D_i \geq 0$ . The value "0" is

because  $g_i$  may be swapped without any improvement in the delay when it is not a part of longest path.

$D_{g_i}^c$  and  $D_{g_i}^b$  is the circuit delay when gate  $g_i$  is implemented in CMOS and BiCMOS respectively.

• Vector  $C = (\Delta C_1, \Delta C_2, \dots, \Delta C_n)$

$$\Delta C_i = C_{q_i}^b - C_{q_i}^c$$

where:

$\Delta C_i$  is the total capacitance increase of the circuit due to changing gate i implementation from CMOS to BiCMOS.

$C_{g_i}^c$  and  $C_{g_i}^b$  is total capacitance of the circuit when  $g_i$  is CMOS and BiCMOS respectively.

Due to non-availability of power dissipation model for BiCMOS, we expressed the changes in power in terms of changes in capacitance. The power of CMOS and BiCMOS gates is proportional to their capacitive load [EBE93].

The problem is to find a subset S of A such that when the nodes in S are implemented by BiCMOS lead to maximum reduction in  $T_{max}$ , while satisfying a threshold constraint on capacitance, that is,

$$\begin{cases} \text{maximize } \sum_{i \in S} \Delta D_i \\ \text{subject to } \sum_{i \in S} \Delta C_i \leq C_T \end{cases}$$

(3.1)

The term  $\sum_{i \in S} \Delta D_i$  reflects the total circuit delay gain due to changing a set S of gates from CMOS to BiCMOS.  $C_T$  is a user specified threshold which represents the maximum allowable total capacitance increase.

The output is:

- S where  $S \subseteq A$ .

- $\Delta D = \sum_{i \in S} \Delta D_i$

- $\Delta C = \sum_{i \in S} \Delta C_i$

If  $T_{max}$  is the initial delay of the circuit, then the final delay:

$$D_F = T_{max} - \Delta D \tag{3.2}$$

Let  $C_I$  be the initial total capacitance. Then the final capacitance is,

$$C_F = C_I - \Delta C \tag{3.3}$$

Next, we shall show that the decision version of COP is NP-Complete.

#### 3.2.1 Is COP in NP?

In order to prove that COP is in NP, we need to find a nondeterministic algorithm that could be used to solve the problem in polynomial time [HS90]. Before doing this, let us present some definitions and concepts. Choice(A) is a function that arbitrarily chooses one of the elements of a set A. Success and Failure are two signals to indicate a successful and unsuccessful completion of the algorithm respectively. The assignment statement  $X \leftarrow Choice(1:n)$  could result in X being assigned any value of the integers in the range [1,n]. There is no rule to specify how this choice is to be made. Whenever there is a set of choices leading to a successful completion then one such set of choices is always made and the algorithm terminates successfully. A nondeterministic algorithm terminates unsuccessfully if and only if there exists no set of choices leading to a success signal [HS90].

For COP, let "0" and "1" represent the choice between CMOS and BiCMOS, and  $\mathcal{X}$  represents a set of these choices. Let M be a maximum objective reduction in the delay. Then we can formulate a nondeterministic algorithm for COP as shown in Figure 3.1. As you can see from the figure that there is no rule of how to guess a solution that leads to a successful termination of the algorithm. The time complexity of this algorithm is O(n).

```

\begin{aligned} & \textbf{algorithm} \ COP(n, M, C_T, \mathcal{X}, \mathcal{D}, \mathcal{C}) \\ & \textbf{for } i \leftarrow 1 \ \textbf{to } n \ \textbf{do} \\ & \quad X_i \leftarrow \textbf{choice}(\mathbf{0}, \mathbf{1}) \\ & \textbf{repeat} \\ & \quad \text{if } \sum_{1 \leq i \leq n} (\Delta D_i \times X_i) < M \ \text{or } \sum_{1 \leq i \leq n} (\Delta C_i \times X_i) > C_T \ \textbf{then failure} \\ & \quad \text{else success} \\ & \quad \textbf{endif} \\ & \textbf{end} \ COP \end{aligned}

```

Figure 3.1: Nondeterministic COP algorithm.

#### 3.2.2 Is COP NP-Complete?

The COP is an NP-Complete problem if it is NP-Hard and belongs to the NP class of problems. In the previous section, we proved that COP is NP. Now let us try to prove that it is NP-Hard. To do so, the following steps need to be carried out: [Baa91]

- 1. Select an NP-Complete problem  $\Pi$ .

- 2. Show that  $\Pi$  is reducible to COP by finding a polynomial function T(x) that transforms (reduces)  $\Pi$  to COP

Let  $\Pi$  denotes the Knapsack problem which is known to be NP-Complete problem [HS90]. The definition of Knapsack problem is as follows: A set of n items is available to be packed into a knapsack with capacity C units. Item i has a profit  $p_i$  and uses up  $s_i$  units of capacity. The problem is to determine the subset I of items which should be packed in order to maximize:

$$\sum_{i \in I} p_i \tag{3.4}$$

such that

$$\sum_{i \in I} s_i \le C$$

Here the solution is represented by the subset  $I \subseteq \{1, ..., n\}$ . Now let us show

that  $\Pi$  is reducible to COP. As we can see there is a correspondence between the input/output of COP and the input/output of  $\Pi$ . That is:

- Both of the problems have an input of n items.

- Item i in COP has  $\Delta D_i$  gain in the delay (profit) which corresponds to the profit  $p_i$  of item i in  $\Pi$ .

- Item i in COP uses  $\Delta C_i$  units of capacity which corresponds to the capacity  $s_i$  of item i in  $\Pi$ .

- The objective of both problems is to find out a subset of items that maximize the total gain (profit).

- Both problems COP and  $\Pi$  are subjected to some constraints of a given capacity threshold,  $C_T$  and C respectively.

Let T(x) be a polynomial reducible function from  $\Pi$  to COP. Then from the previous correspondence we can deduce the following:

$$T(C) = C_T \tag{3.5}$$

$$T(s_1, s_2, \dots, s_n) = \Delta C_1, \Delta C_2, \dots, \Delta C_n$$

(3.6)

$$T(p_1, p_2....p_n) = \Delta D_1, \Delta D_2, ...\Delta D_n$$

(3.7)

It is clear that T(x) is one\_to\_one function of O(n) time complexity. This means that  $\Pi$  is reducible to COP. Hence COP is NP-Hard problem. Since COP is NP-Hard and at the same time it belongs to NP class of problems, then it is NP-Complete.

The above result justifies searching for a heuristic solution to this problem. The heuristic solution adopted is described next.

# 3.3 The Proposed Solution Technique

The proposed solution technique consists of three phases:

- 1. Generate critical paths of the input circuit.

- 2. Eliminate false paths from the generated critical paths.

- 3. Apply TS algorithm to select a subset S of BiCMOS gates among those covered by the sensitizable critical paths so as to minimize delay while satisfying a threshold constraint on circuit capacitance.

The general structure of the process is shown in Figure 3.2. In the following sections each phase will be described in more details.

Figure 3.2: General structure of the proposed solution technique.

#### 3.3.1 Phase I

As we have seen in Section 2.3.1, it is not feasible and even not necessary to consider all the paths in the optimization process. Instead, optimizing only the longest sensitizable paths eases the problem and decreases the computation time considerably. Many techniques have been proposed to find the longest sensitizable paths as described earlier. Since our main goal emphasizes on the output of the optimization process, we can choose any sensitization method which generates reasonable results. Nevertheless,  $\alpha$ -critical algorithm [AF95], which generates critical paths including false paths, has been selected because of the following reasons:

- It can easily be interfaced with the adopted false path checking algorithm.

- The algorithm considers the delay of interconnections resulting in more accurate timing prediction.

- It is flexible in generating as many critical paths as required by the user.

- The tools implementing this algorithm are available to us.

The detailed description of  $\alpha$ -critical algorithm and its application on some benchmark circuits are presented in the following chapter.

#### 3.3.2 Phase II

After generating all critical paths for a given circuit, these paths are checked via false path checking algorithm to eliminate the false paths. This step is necessary to speed up the optimization process by minimizing the input population as well as providing accurate timing. As mentioned earlier, many techniques have been proposed for this purpose. We have chosen the algorithm reported in [YDG89] for the following reasons:

- It is easy to interface with the  $\alpha$ -critical algorithm.

- It is based on dynamic criterion by which more accurate results are generated.

- It is easy to implement.

- The algorithm focuses on the general false path problem, which detects whether a given path (not necessarily the longest one) is false or not. In this case, any number of paths having the same delay can be detected. This capability is not available in most of the other techniques.

The detailed description of this algorithm and its application on some benchmark circuits are presented in Chapter 4.

#### 3.3.3 Phase III

The main contribution of our work is included in this phase which covers the process of optimal selection of gates required to be implemented in BiCMOS technology. The input of this process is the output of the second phase in which the longest sensitizable paths are generated. The goal is to replace some of the CMOS gates by BiCMOS gates in order to optimize the circuit for delay and capacitance. The output is a mixed CMOS/BiCMOS circuit with optimum cost. Since this process involves a lot of processing and data manipulation, the required optimization algorithm has to be correct, effective, and efficient. TS algorithm has proven to be efficient and powerful in dealing with very complex problems. In addition, we have chosen TS for the following reasons:

- It is modular and easy to implement.

- Its ability to handle additional considerations such as constraints not encompassed by the original problem formulation.

- It is able to escape the trap of local optimality.

The details of this algorithm and how it has been applied on COP are presented in Chapter 5.

### 3.4 Summary

In this chapter, the formal definition of COP has been presented. We have proven that the decision version of this problem belongs to the class of NP-Complete problems which require heuristic techniques to find sub-optimal solutions. Our proposed solution technique to this problem consists of three phases. The first and second phase aim at finding the K longest sensitizable paths for a given circuit because circuit delay is determined by the longest sensitizable paths. The third phase is the core phase which includes the application of TS algorithm.

# Chapter 4

# Timing Analysis and False Path

# **Problem**

### 4.1 Introduction

This chapter covers the timing analysis and false path problem. In Section 2 of this chapter, some timing analysis concepts and a detailed description of  $\alpha$ -critical path algorithm, which represents the first phase in the proposed solution technique to COP, are presented and illustrated with an example. The second phase of our proposed solution technique is the elimination of false paths from the generated critical paths. This phase is covered in Section 3 where some aspects of false path problem and drawbacks of D-algorithm to detect false paths are explained with an illustrative example. In addition, this section describes in detail the adopted false

path detection algorithm and the method of implementation. The experimental results of applying both  $\alpha$ -critical path and false path detection algorithms are presented and discussed in Section 4. Then we conclude in Section 5. We begin with the discussion on some timing analysis concepts that have been taken from [AF95] and summarized for completeness.

# 4.2 Timing Analysis and $\alpha$ -Critical Approach

The delay of the circuit is determined by its longest sensitizable paths. Therefore, to verify and optimize the circuit timing, the focus should be on predicting the timing critical paths only. A path  $\pi$  is classified as critical if its total delay,  $T_{\pi}$ , is very close to its latest required arrival time  $LRAT_{\pi}$ . If  $T_{\pi}$  exceeds  $LRAT_{\pi}$ , path  $\pi$  becomes a long path. The path delay consists of two components: the logic delay which is known prior to layout, and the interconnect delay which is unknown. In VLSI designs, the interconnect delay is a major part of the overall path delay. Therefore it is very important for pre-layout timing analysis to predict the interconnect delay requirements. The interconnect capacitance is a key element in the total interconnect delay [AF95]. The  $\alpha - critical$  algorithm aims at predicating the interconnect delay requirements of a given circuit by estimating the delay of the longest paths in the circuit. Before we describe this algorithm, we recall from [AF95] some definitions and equations proposed to compute the path delay.

Let  $\pi = \{v_1, v_2, \dots, v_p\}$  be a path in the circuit graph, where  $v_1$  and  $v_p$  are the source and sink cells. The total delay on  $\pi$  is given by,

$$T_{\pi} = \sum_{i=1}^{p-1} (CD_{v_i} + ID_{v_i}) \tag{4.1}$$

where,  $CD_{v_i}$  is the switching delay of cell  $v_i$  and  $ID_{v_i}$  is the interconnect delay of the net driven by cell  $v_i$ .

The switching delay may be expressed as follows,

$$CD_{v_i} = BD_{v_i} + LF_{v_i} \times AcL_{v_i} \tag{4.2}$$

where,  $BD_{v_i}$  is the base (intrinsic) delay of cell  $v_i$  in nanoseconds,  $LF_{v_i}$  is the load factor of the output pin of the driving cell  $v_i$ , expressed in units of time per unit capacitance, and  $AcL_{v_i}$  is the summation of input capacitance of fan-out gates of cell  $v_i$ .

The interconnection delay may be expressed as follows,

$$ID_{v_i} = LF_{v_i} \times C_{v_i} \tag{4.3}$$

where,  $C_{v_i}$  is the total interconnect capacitance (area + fringe) of the net driven by cell  $v_i$ .

The interconnect capacitance  $C_{v_i}$  is estimated using data from past designs as follows. The average and standard deviation of net length for different types of nets (2-pin, 3-pin, ..., m-pin) are collected from past designs of similar complexity<sup>1</sup>.

<sup>1</sup>this classification helps reduce the sample variance around the mean

These are transformed into interconnect capacitances. Let  $\overline{C_{v_i}}$  and  $s_{v_i}$  be the estimated expected interconnect capacitance and standard deviation of the net driven by cell  $v_i$ . Then, the expected interconnect delay  $\overline{ID_{v_i}}$  of net  $v_i$  and its corresponding variance  $S_{v_i}^2$  are estimated as follows:

$$\overline{ID_{v_i}} = LF_{v_i} \times \overline{C_{v_i}} \quad ; \quad S_{v_i}^2 = LF_{v_i}^2 \times S_{v_i}^2 \tag{4.4}$$

Under the assumption of statistical independence between the nets, the expected delay and variance on any path  $\pi$  can be expressed as follows,

$$T_{\pi} = \sum_{i=1}^{p-1} (CD_{v_i} + \overline{ID_{v_i}}) \; ; \; S_{\pi}^2 = \sum_{i=1}^{p-1} S_{v_i}^2$$

(4.5)

Let  $T_{\text{max}}$  be the expected delay of the longest path in the circuit, that is,

$$T_{\max} = \max_{\pi \in \Pi} (T_{\pi}) \tag{4.6}$$

where  $\Pi$  is the set of all paths in the circuit graph G.

#### 4.2.1 Description of $\alpha$ -Critical Algorithm

The  $\alpha$ -critical approach is based on the following definition:

**Definition:** A given path  $\Pi$ , with overall delay  $T_{\Pi}$ , is  $\alpha$ -critical iff:

$$T_{\Pi} + \alpha \times \sqrt{S_{\Pi}^2} \ge T_{max} \tag{4.7}$$

For a user specified  $\alpha$ , the  $\alpha$ -critical approach enumerates all paths which satisfy Equation 4.7. The parameter  $\alpha$  is interpreted as a confidence level.  $T_{\Pi} + \alpha \times \sqrt{S_{\Pi}^2}$

means that we are  $\alpha \times \sqrt{S_{\Pi}^2}$  ns confident that path  $\Pi$  is critical. The higher  $\alpha$  is, the larger the number of reported paths will be, and the higher is the probability of capturing all the critical paths [AF95].

The input circuit to the algorithm is modeled as an acyclic directed graph G = (V, E), where V is the set of vertices representing the signal nets and E is the set of edges representing the nodes. To trace all vertices and enumerate the paths, Depth First Search with pruning is applied. The algorithm starts with backward trace from primary outputs to primary inputs. During this step, for each vertex v the maximum delay  $MAXD_v$  and the maximum variance  $MAXV_v$  between the vertex and the primary outputs are computed. Then forward trace is performed to enumerate the critical paths. During this step, when the search reaches a vertex v along the partial path  $\Pi$  with partial delay  $T_{\Pi}$  and variance  $S_{\Pi}^2$ , the following criticality test is made:

$$T_{\Pi} + MAXD_{v} + \alpha \times \sqrt{S_{\Pi}^{2} + MAXV_{v}} \ge T_{max}$$

(4.8)

If the test is positive, meaning that the partial path  $\Pi$  is  $\alpha$ -critical, the search continues. If not, this means that the partial path  $\Pi$  is not  $\alpha$ -critical. Hence all paths starting with this partial path are not  $\alpha$ -critical too. Therefore, it is not necessary to continue the search. In this case, the algorithm stops and backtrace to the predecessor vertex (pruning the search). Once all the  $\alpha$ -critical paths are found, they are sorted in descending order and then reported as an output [AF95].

#### 4.2.2 Example

Let us give a simple example that demonstrates how the algorithm works. Figure 4.1 shows a simple combinational circuit. Assume that for 2-pin and 3-pin nets, the average interconnect capacitance,  $\bar{c}$ , is 0.04966 pF and 0.06428 pF respectively, and the standard deviation, s, is 0.03819 pF and 0.02698 pF respectively. The values of base delay, load factor and input capacitance of the gates are taken from Table 7.2.3 in Appendix A. Using the equations stated earlier with the confidence level set to 25, we obtain the following critical paths:

•

$$P_1 = C - 1 - E - 2 - F - 3 - H - 5 - I - 6 - Y$$

.  $T_{p_1} = 14.056$  ns,  $S_{p_1}^2 = 0.128$

•

$$P_2 = D - 2 - F - 3 - H - 5 - I - 6 - Y$$

.  $T_{p_2} = 10.958$  ns,  $S_{p_2}^2 = 0.112$

•

$$P_3 = B - 3 - H - 5 - I - 6 - Y$$

.  $T_{p_3} = 7.853$  ns,  $S_{p_3}^2 = 0.090$

#### 4.3 False Path Problem

The timing analysis based techniques ignores the functionality of the circuit. These techniques aim at finding the longest paths either sensitizable (true) or unsensitizable (false). The presence of false paths has many undesirable effects including loss of accuracy and waste of optimization effort. Therefore, it is essential to eliminate false paths from the critical ones. Many techniques have been proposed to serve this purpose. However, most of them are based on the D-algorithm approach which is

Figure 4.1: A simple combinational circuit.

applied mainly in testing a circuit for stuck\_at\_fault. During a signal propagation, all other signals are assumed to be stable. When this algorithm is used for false path detection, stableness assumption remains. For most of the time this assumption may be true, especially in detecting the single longest false path. When general path is considered or several longest paths with same delay exist in the circuit, this assumption may not work. The following example demonstrates the idea. Figure 4.2 shows a simple combinational circuit in which the delay of all gates is assumed equal 1 ns, the delay of all signals is assumed equal 0 ns, and all the primary inputs are stabilized at 0 ns. Let  $P_1 = B1 - 1 - F - 3 - G - 4 - H - 5 - Y$  and  $P_2 = C1 - 1 - F - 3 - G - 4 - H - 5 - Y$ . Both  $P_1$  and  $P_2$  are the longest paths with the same delay 4 ns. Using D-algorithm to detect whether path  $P_1$  is false or not, we set signals C1 = 1, A = 0, D = 0 & E = 1 respectively to allow the signals propagate along path  $P_1$ . Then new values of signals are induced from those signals. Since C1 = 1 = C = C2, C2 is set to 1. Since gate 2 is NOR and one of its inputs is 1, then E becomes 0. However the initial value of E is 1 which makes Einconsistent. Therefore we claim  $P_1$  to be false. Using a similar argument, we can conclude that  $P_2$  is false too. Based on that the worst delay of the circuit is 3 ns instead of 4 ns.

Now let us apply the input (A = 1, B = 0, C = 0, D = 0), we get F = 0 & E = 1 at 1 ns, G = 1 at 2 ns, and H = 1 at 3 ns. Since E = 1 is a non-control value to gate 5, the output Y of gate 5 can not be decided until H is stabilized. Signal H is

Figure 4.2: Another simple combinational circuit.

stabilized at 3 ns, hence signal Y is stabilized at 4 ns. This condition shows that the worst delay of the circuit is 3 ns which conflicts with the result of the D-algorithm.

#### 4.3.1 False Path Detection Algorithm