# DIGITAL CIRCUIT DESIGN THROUGH SIMULATED EVOLUTION

BY

## UTHMAN SALEM AL-SAIARI

A Thesis Presented to the DEANSHIP OF GRADUATE STUDIES

#### KING FAHD UNIVERSITY OF PETROLEUM & MINERALS

DHAHRAN, SAUDI ARABIA

\* TANDAR TO THE TOTAL TO THE TH

In Partial Fulfillment of the Requirements for the Degree of

## MASTER OF SCIENCE

In COMPUTER ENGINEERING

November 2003

UMI Number: 1418913

#### **INFORMATION TO USERS**

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleed-through, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

#### UMI Microform 1418913

Copyright 2004 by ProQuest Information and Learning Company.

All rights reserved. This microform edition is protected against unauthorized copying under Title 17, United States Code.

ProQuest Information and Learning Company 300 North Zeeb Road P.O. Box 1346 Ann Arbor, MI 48106-1346

# KING FAHD UNIVERSITY OF PETROLEUM & MINERALS DHAHRAN 31261, SAUDI ARABIA DEANSHIP OF GRADUATE STUDIES

This thesis, written by

#### UTHMAN SALEM AL-SAIARI

under the direction of his Thesis Advisor and approved by his Thesis Committee, has been presented to and accepted by the Dean of Graduate Studies, in partial fulfillment of the requirements for the degree of

#### MASTER OF SCIENCE IN COMPUTER ENGINEERING

Thesis Committee

Prof. Sadiq M. Sait (Chairman

Prof. Mostafa Abd – El – Barr (Co – Chairman)

Dr. Muhammad Farrukh Khan (Member)

Prof. Sadiq M. Sait Department Chairman

Prof. Osama A. Jannadi Dean of Graduate Studies

8/12/2003 Date To my father, God's blessings be upon his grave

To my mother for her prayers all nights

To my dear wife for her love and patience.

## ACKNOWLEDGEMENTS

First of all, all sincere praises and thanks are due to our God, Allah (SWT), who created us and guided us to this great religion, i.e., the Islam. No one can thank God as he deserves because of his limitless blessings on us. May God's peace and blessings be upon his prophet Mohammad who said<sup>1</sup>: The person who does not thank people, does not thank God as well.

Thanks to my advisor, Prof. Sadiq M. Sait, who was very helpful during all the phases of this work. This thesis is never possible without the support, encouragement and the valuable time spent by my advisor in bringing this work into existence. Also, thanks to Prof. Mostafa Abd-El-Barr, my co-advisor, for his help during the course of this thesis. Thanks are also due to our great department, Computer Engineering, and our great university, KFUPM, for the valuable support. Also, I would like to express my deepest thanks to every instructor who contributed in building my knowledge and experience. Thanks are also due to my colleagues, especially Mr. Sarif Bambang, who did not hesitate in providing me with any kind of help I needed. I would also to acknowledge the help of Dr. Carlos A. Coello for his valuable discussion during the course of this thesis. Also, I want to thank Syed Sanaullah for his help in the arrangement and finalizing the copying and printing of

<sup>&</sup>lt;sup>1</sup>This is only a translation of the meaning of what he said. He originally said so in Arabic. May peace and blessings be upon him.

this thesis.

I also thank my great parents who provided and supported me all the way. Thanks to them and may God bless them. Last but not least, thanks to my great dear wife who supported me with love and patience. She was really very patient during my work and she always inspired me to finish my work as quickly as possible. Thanks to her very much. Finally, thanks to everybody who contributed to this achievement in a direct or an indirect way.

## Contents

|            | AC  | KNOWLEDGEMENTS      | iv  |

|------------|-----|---------------------|-----|

|            | LIS | T OF TABLES         | xii |

|            | LIS | T OF FIGURES        | xv  |

|            | AB  | STRACT (ENGLISH)    | xix |

|            | AB  | STRACT (ARABIC)     | xx  |

| - Personal | INT | TRODUCTION          | 1   |

|            | 1.1 | Logic Design        | 2   |

|            | 1.2 | Problem Definition  | 6   |

|            | 1.3 | Related Work        | 7   |

|            | 1.4 | Motivation          | . 8 |

|            | 1.5 | Thesis Organization | 10  |

| 2          | BA  | CKGROUND            | 11  |

|   | 2.1                             | Conventional Logic Design (CLD)                      | 11                         |

|---|---------------------------------|------------------------------------------------------|----------------------------|

|   |                                 | 2.1.1 Two-level Boolean Functions                    | 13                         |

|   |                                 | 2.1.2 Multilevel Boolean Functions                   | 13                         |

|   |                                 | 2.1.3 Reed-Muller and Exclusive-OR Logic             | 15                         |

|   | 2.2                             | Logic Design Optimization                            | 15                         |

|   | 2.3                             | Multi-objective Optimization                         | 16                         |

|   | 2.4                             | Fuzzy Logic                                          | 18                         |

|   |                                 | 2.4.1 Fuzzy Set Theory                               | 19                         |

|   |                                 | 2.4.2 Multi-objective Optimization Using Fuzzy Logic | 22                         |

|   | 2.5                             | Concluding Remarks                                   | 24                         |

|   |                                 |                                                      |                            |

| 3 | EV                              | OLUTIONARY LOGIC DESIGN (ELD)                        | 25                         |

| 3 | EV(                             | OLUTIONARY LOGIC DESIGN (ELD)  Genetic Algorithm     |                            |

| 3 |                                 |                                                      | 28                         |

| 3 | 3.1                             | Genetic Algorithm                                    | 28<br>29                   |

| 3 | 3.1                             | Genetic Algorithm                                    | 28<br>29<br>32             |

| 3 | 3.1                             | Genetic Algorithm                                    | 28<br>29<br>32<br>32       |

| 3 | 3.1                             | Genetic Algorithm                                    | 28<br>29<br>32<br>32<br>35 |

| 3 | 3.1<br>3.2<br>3.3               | Genetic Algorithm                                    | 28<br>29<br>32<br>32<br>35 |

| 3 | 3.1<br>3.2<br>3.3<br>3.4<br>3.5 | Genetic Algorithm                                    | 28<br>29<br>32<br>32<br>35 |

|   |     | 4.1.1  | Evaluation                                               | 43 |

|---|-----|--------|----------------------------------------------------------|----|

|   |     | 4.1.2  | Selection                                                | 44 |

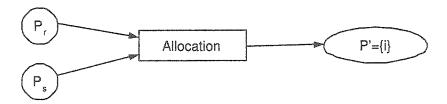

|   |     | 4.1.3  | Allocation                                               | 45 |

|   |     | 4.1.4  | Initialization Phase                                     | 46 |

|   | 4.2 | Comp   | arison of Simulated Evolution and Genetic Algorithm (GA) | 46 |

|   | 4.3 | Concl  | uding Remarks                                            | 48 |

| 5 | SIN | IULAI  | TED EVOLUTION ALGORITHM (SIME) FOR LOGIC                 |    |

|   | DE  | SIGN   |                                                          | 49 |

|   | 5.1 | Introd | luction                                                  | 50 |

|   | 5.2 | Circui | t Encoding                                               | 51 |

|   | 5.3 | Propo  | sed SimE Algorithm: Parameters and Operators             | 54 |

|   |     | 5.3.1  | Initialization Phase and Parameters                      | 55 |

|   |     | 5.3.2  | Selection Operator                                       | 56 |

|   |     | 5.3.3  | Allocation Operator                                      | 57 |

|   |     | 5.3.4  | Evaluation Function                                      | 59 |

|   | 5.4 | Hybrid | d SimE Using Tabu Search (TS)                            | 60 |

|   |     | 5.4.1  | Tabu Search (TS)                                         | 60 |

|   |     | 5.4.2  | Tabu Search for Logic Design                             | 61 |

|   |     | 5.4.3  | Hybrid SimE Algorithm                                    | 63 |

|   | 55  | Conclu | iding Romarks                                            | 61 |

| 6 | GO  | ODNI   | ESS MEASUREMENTS                          | 65  |

|---|-----|--------|-------------------------------------------|-----|

|   | 6.1 | Propo  | osed Goodness Measures                    | 65  |

|   |     | 6.1.1  | Pattern Based Goodness                    | 66  |

|   |     | 6.1.2  | Multilevel Logic Based Goodness           | 68  |

|   | 6.2 | Optin  | nization Goodness Measure                 | 75  |

|   |     | 6.2.1  | Area Estimation                           | 76  |

|   |     | 6.2.2  | Delay Estimation                          | 77  |

|   |     | 6.2.3  | Power Consumption Estimation              | 79  |

|   | 6.3 | Weigh  | nted Sum Fitness Function Calculation     | 81  |

|   |     | 6.3.1  | Functional Fitness                        | 81  |

|   |     | 6.3.2  | Objective Fitness                         | 81  |

|   | 6.4 | Fuzzy  | Fitness Function Calculation              | 83  |

|   |     | 6.4.1  | Functional Fitness                        | 83  |

|   |     | 6.4.2  | Objective Fitness                         |     |

|   | 6.5 | Concl  | uding Remarks                             | 91  |

| 7 | EXI | PERIN  | MENTS AND RESULTS                         | 92  |

|   | 7.1 | Exper  | imental Setup                             | 92  |

|   | 7.2 | Perfor | mance of Different Goodness Measures      | 94  |

|   | 7.3 | Effect | of Hybrid SimE on the Quality of Solution | 98  |

|   | 7.4 | Effect | of Different Optimization Objectives      | 100 |

|   | 7.5  | Concluding Remarks                               | 109 |

|---|------|--------------------------------------------------|-----|

| 8 | CO:  | MPARISON WITH EXISTING TECHNIQUES                | 110 |

|   | 8.1  | Comparison with Existing ELD Techniques          | 110 |

|   | 8.2  | Comparison with Existing Conventional Techniques | 112 |

|   | 8.3  | Comparison with Other Techniques                 | 120 |

|   |      | 8.3.1 Comparison with Tabu Search                | 120 |

|   |      | 8.3.2 Comparison with ACO [35]                   | 122 |

|   | 8.4  | Concluding Remarks                               | 128 |

| 9 | CO   | NCLUSION AND FUTURE DIRECTIONS                   | 129 |

|   | 9.1  | Conclusion                                       | 130 |

|   | 9.2  | Future Directions                                | 131 |

|   | AP]  | PENDIX                                           | 132 |

| A | File | Format and Circuit Used as Test Cases            | 132 |

|   | A.1  | Library File Format                              | 132 |

|   | A.2  | Input File Format                                | 133 |

|   | A.3  | Randomly Generated Circuits                      | 135 |

|   | A.4  | Benchmark Circuits                               | 135 |

|   | BIB  | BLIOGRAPHY                                       | 137 |

VITA 145

## List of Tables

| 3.1 | Possible cell functions in Miller [28, 29]                            |

|-----|-----------------------------------------------------------------------|

| 5.1 | All gate types used by SimE                                           |

| 7.1 | Summary of circuits used for the experiments                          |

| 7.2 | Results comparison between SimE-G1 and SimE-G2 97                     |

| 7.3 | Improvements in execution time in SimE-G2 over SimE-G1 98             |

| 7.4 | Results comparison between SimE-G2 and Hybrid SimE-G2 99              |

| 7.5 | Improvements in execution time in SimE-G2 over Hybrid SimE-G2 100     |

| 7.6 | Area for selected circuits using SimE-G1 with the four set of experi- |

|     | ments                                                                 |

| 7.7 | Area for selected circuits using SimE-G2 with the four set of experi- |

|     | ments                                                                 |

| 7.8 | Delay for selected circuits using SimE-G1 with the four set of exper- |

|     | iments                                                                |

| 7.9  | Delay for selected circuits using SimE-G2 with the four set of exper-      |

|------|----------------------------------------------------------------------------|

|      | iments                                                                     |

| 7.10 | Power for selected circuits using SimE-G1 with the four set of exper-      |

|      | iments                                                                     |

| 7.11 | Power for selected circuits using SimE-G2 with the four set of exper-      |

|      | iments                                                                     |

| 8.1  | Comparison with Coello [8] technique in terms of area, delay and power.111 |

| 8.2  | Comparison with Coello's GA algorithm in terms of execution time [7].112   |

| 8.3  | Comparison of SimE-G1 and SIS in area optimization for single out-         |

|      | put circuits                                                               |

| 8.4  | Comparison of SimE-G1 and SIS in area optimization for multiple            |

|      | output circuits                                                            |

| 8.5  | Comparison of SimE-G2 and SIS in area optimization for single out-         |

|      | put circuits                                                               |

| 8.6  | Comparison of SimE-G2 and SIS in area optimization for multiple            |

|      | output circuits                                                            |

| 8.7  | Comparison of SimE-G2 and SIS in delay optimization for single out-        |

|      | put circuits                                                               |

| 8.8  | Comparison of SimE-G2 and SIS in delay optimization for multiple           |

|      | output circuits 118                                                        |

| 8.9  | Comparison of TS and SimE-G2 in area and power optimization with |

|------|------------------------------------------------------------------|

|      | delay constraint                                                 |

| 8.10 | Comparison with TS in terms of execution time                    |

| 8.11 | Comparison of ACO and SimE-G2 considering area optimization 125  |

| 8.12 | Comparison of ACO and SimE-G2 considering delay optimization 126 |

| 8 13 | Comparison of ACO and SimE-G2 considering power optimization 127 |

## List of Figures

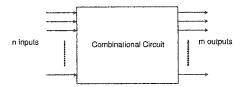

| 1.1 | Block diagram of a combinational circuit                               | 2  |

|-----|------------------------------------------------------------------------|----|

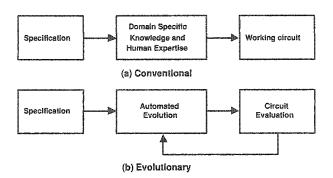

| 1.2 | Conventional versus evolutionary design methodology                    | 3  |

| 1.3 | Evolutionary design process [28]                                       | 5  |

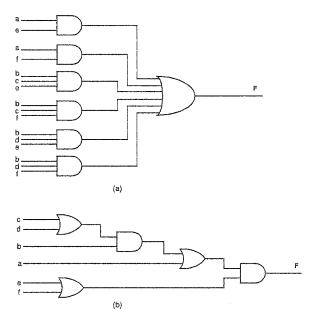

| 2.1 | Representation of a boolean function in (a) in two-level logic (b) in  |    |

|     | multi-level logic                                                      | 14 |

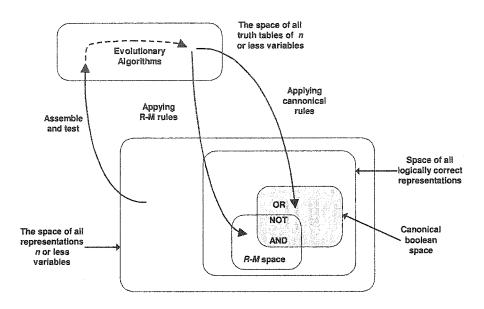

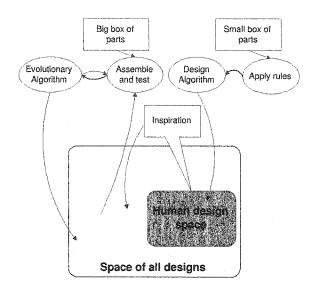

| 3.1 | Conventional design versus evolutionary design with assemble-and-test. | 30 |

| 3.2 | How "assemble-and-test" reaches the unknown regions of the space       |    |

|     | of all representations                                                 | 31 |

| 3.3 | Chromosome representation in Hounsell [20]                             | 33 |

| 3.4 | Macro blocks and its genotype representation in Hounsell [20]          | 33 |

| 3.5 | Chromosome representation in Miller [28, 29]                           | 33 |

| 3.6 | Example of genotype-phenotype mapping in Miller [28, 29]               | 35 |

| 3.7 | Representation of gene in chromosome in Coello [7, 8]                  | 35 |

| 4.1  | Simulated Evolution algorithm [21, 34]                     | 42 |

|------|------------------------------------------------------------|----|

| 4.2  | Evaluation                                                 | 43 |

| 4.3  | Selection.                                                 | 44 |

| 4.4  | Selection in the SimE of Figure 4.1                        | 44 |

| 4.5  | Allocation                                                 | 45 |

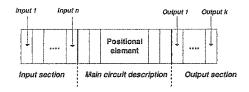

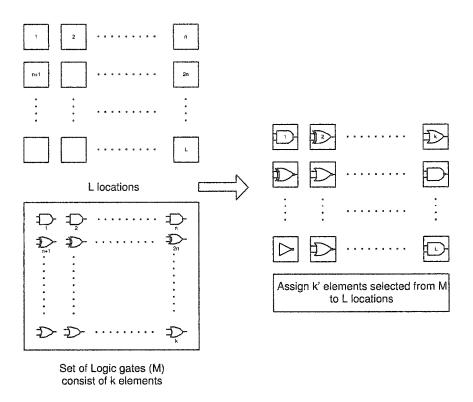

| 5.1  | Representation of the digital logic design problem in SimE | 51 |

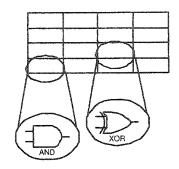

| 5.2  | The matrix representation of a circuit.                    | 52 |

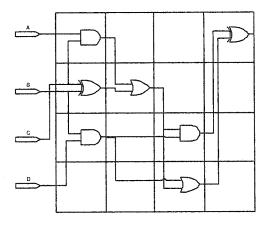

| 5.3  | An example of a 4 input circuit                            | 52 |

| 5.4  | Representation of individual in matrix                     | 54 |

| 5.5  | Selection in the SimE                                      | 57 |

| 5.6  | Allocation function in SimE                                | 58 |

| 5.7  | Evaluation function in SimE                                | 59 |

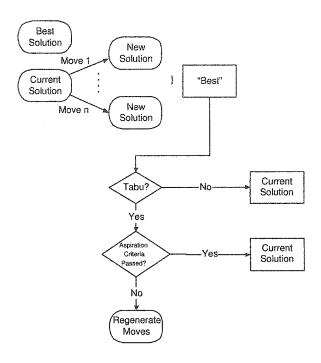

| 5.8  | Flow chart of the tabu search algorithm [34]               | 61 |

| 5.9  | Tabu Search algorithm (TS)                                 | 62 |

| 5.10 | Hybrid Simulated Evolution algorithm                       | 63 |

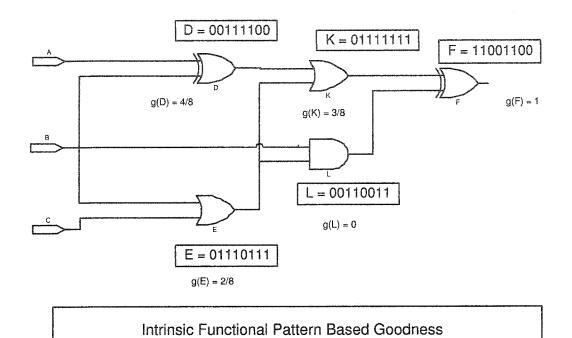

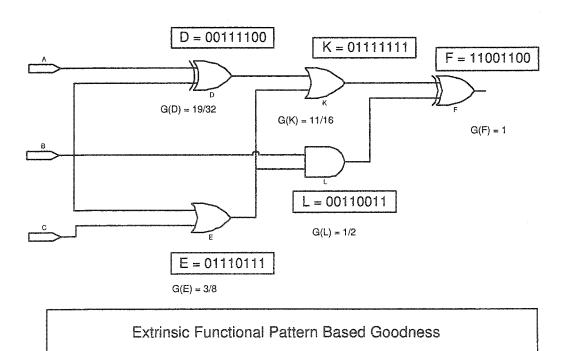

| 6.1  | Extrinsic functional pattern based goodness                | 67 |

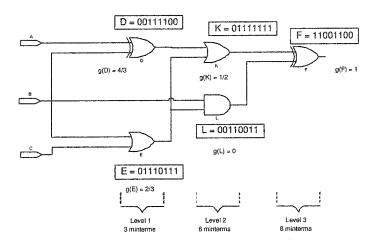

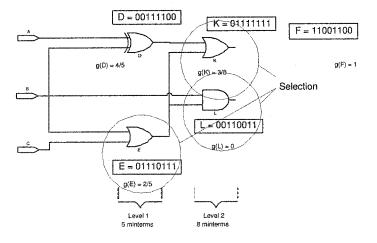

| 6.2  | An example on the pattern based goodness measure           | 69 |

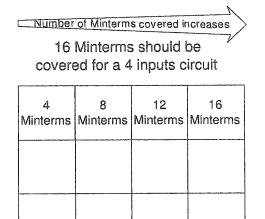

| 6.3  | Multilevel logic goodness assumption                       | 73 |

| 61   | An example on the multilevel goodness measure first sten   | 7/ |

| 6.8 | An example on the multilevel goodness measure after adjusting the     |     |

|-----|-----------------------------------------------------------------------|-----|

|     | number of columns                                                     | 74  |

| 6.0 | 6 Global optimization goodness cost function                          | 76  |

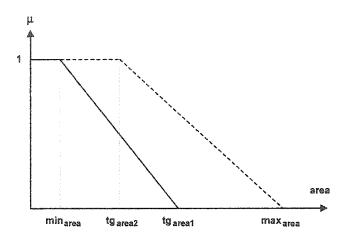

| 6.  | 7 Membership function for area                                        | 86  |

| 6.8 | 8 Membership function for delay                                       | 87  |

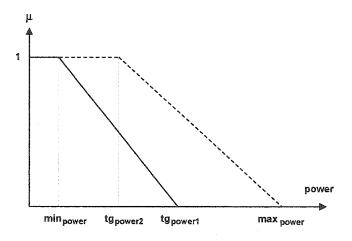

| 6.9 | 9 Membership function for power                                       | 89  |

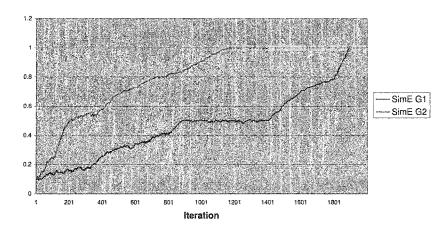

| 7.3 | 1 Fitness function for SimE-G1 and SimE-G2 for 4 inputs circuit (cir- |     |

|     | cuit2)                                                                | 95  |

| 7.5 | 2 Fitness function for SimE-G1 and SimE-G2 for mul3                   | 96  |

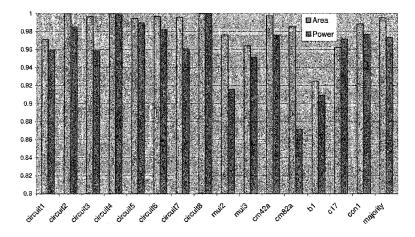

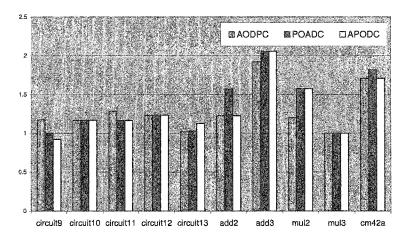

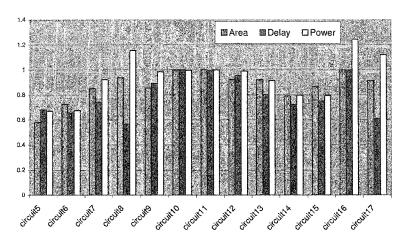

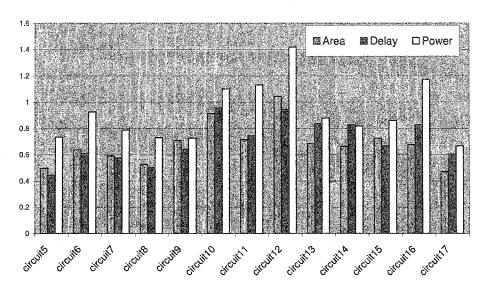

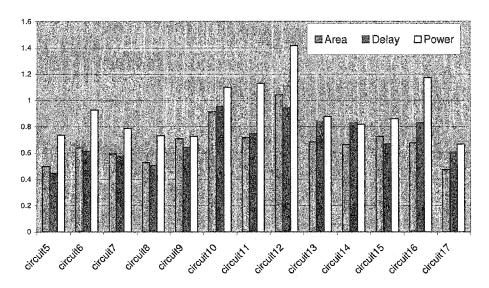

| 7.3 | Normalized area and power of SimE-G2 to the area and power of         |     |

|     | SimE-G1                                                               | 97  |

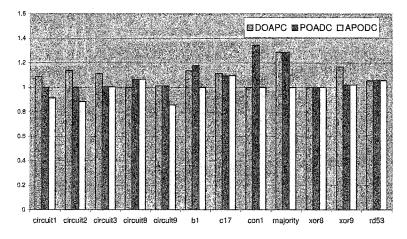

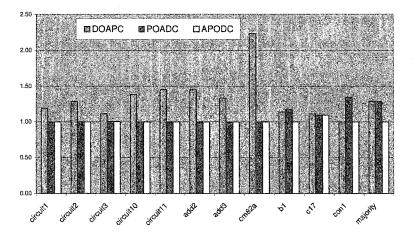

| 7.4 | 4 Normalized area of SimE-G1 (DOAPC, POADC, APODC) to the             |     |

|     | area of SimE-G1 considering area optimization (AODPC) 1               | L02 |

| 7.  | Normalized area of SimE-G2 (DOAPC, POADC, APODC) to the               |     |

|     | area of SimE-G2 considering area optimization (AODPC)                 | l03 |

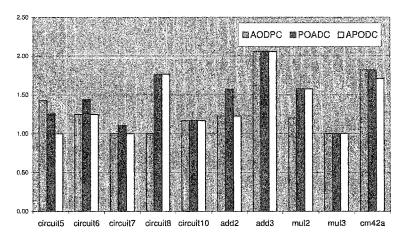

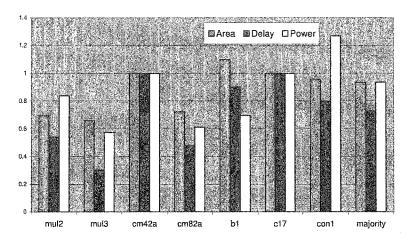

| 7.6 | 6 Normalized delay of SimE-G1 to the delay of SimE-G1 considering     |     |

|     | delay optimization                                                    | 105 |

| 7.  | 7 Normalized delay of SimE-G2 to the delay of SimE-G2 considering     |     |

|     | delay optimization                                                    | 106 |

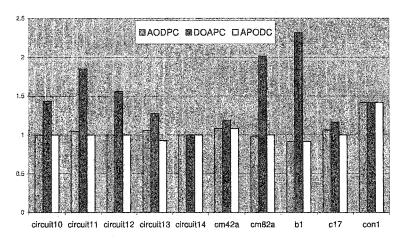

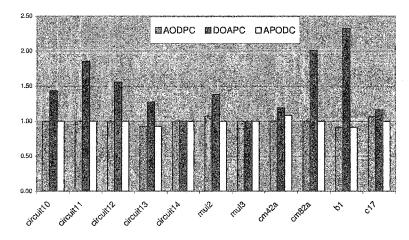

| 7.8 | Normalized power of SimE-G1 to the power of SimE-G1 considering    |     |

|-----|--------------------------------------------------------------------|-----|

|     | power optimization                                                 | 107 |

| 7.9 | Normalized power of SimE-G2 to the power of SimE-G2 considering    |     |

|     | power optimization                                                 | 107 |

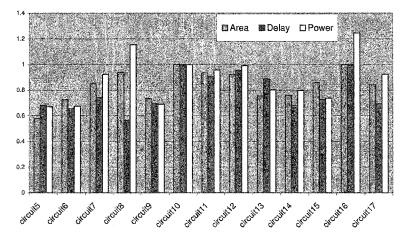

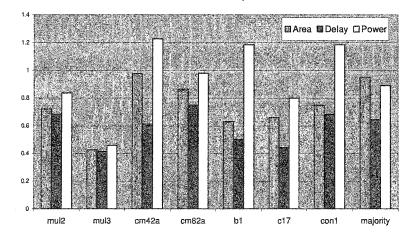

| 8.1 | Results of SimE-G1 with AODPC for single output functions, nor-    |     |

|     | malized to SIS.                                                    | 114 |

| 8.2 | Results of SimE-G1 with AODPC for multiple outputs functions, nor- |     |

|     | malized to SIS                                                     | 115 |

| 8.3 | Results of SimE-G2 with AODPC for single output functions, nor-    |     |

|     | malized to SIS.                                                    | 116 |

| 8.4 | Results of SimE-G2 with AODPC for multiple outputs functions, nor- |     |

|     | malized to SIS.                                                    | 117 |

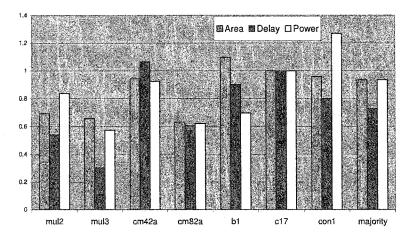

| 8.5 | Results of SimE-G2 with DOAPC for single outputs functions, nor-   |     |

|     | malized to SIS                                                     | 119 |

| 8.6 | Results of SimE-G2 with DOAPC for multiple outputs functions, nor- |     |

|     | malized to SIS                                                     | 119 |

| 87  | Results of SimE-G2 with APODC normalized to TS                     | 199 |

#### THESIS ABSTRACT

Name:

Uthman Salem Al-Saiari

Title:

DIGITAL CIRCUIT DESIGN THROUGH

SIMULATED EVOLUTION

Major Field:

COMPUTER ENGINEERING

Date of Degree:

November 2003

Evolutionary computation presents a new paradigm shift in hardware design and synthesis. The new paradigm is expected to radically change the design procedure such that new possibilities for discovering novel designs and/or more efficient circuits can emerge. In this thesis, Simulated Evolution (SimE) algorithm is used for combinational logic design. SimE algorithm consists of three steps: evaluation, selection and allocation. Two goodness measures are designed to guide the selection and allocation steps of SimE. Area, power and delay are considered in the optimization of circuits. The performance of the proposed algorithm is evaluated using selected ISCAS'85 benchmark and a set of randomly generated circuits. The results obtained are compared to other techniques in terms of power, area and delay. It is shown that the results of the proposed techniques are better in terms of quality and time.

**Keywords:** Evolutionary Circuit Design, Logic Synthesis, Simulated Evolution, Combinatorial Optimization, Multiobjective Optimization, Fuzzy Logic.

#### MASTER OF SCIENCE DEGREE

King Fahd University of Petroleum & Minerals, Dhahran, Saudi Arabia November 2003

## ملخص الرسالة

الأسم : عثمان سالم الصبيعري

عنوان الدراسة: تصميم الدوائر الرقميه من خلال التطور المحاكى

التخصص : هنسة الحاسب الآلي

تاريخ التخرج: نوفمبر ٢٠٠٣

يقدّم الحساب الارتقائي تحوّل جذري جديدًا في تصميم الدوائر الرقميه. التحول الجذري الجديد سيغير طريقة التصميم للدوائر الكهربائيه مما سيؤدى الى اكتشاف تصاميم فريده واكثر عمليه. في هذه الرساله, خوارزم التطور المحاكى استخدمت في تصميم الدوائر الكهربائيه. تتكون خوارزم التطور المحاكى من ثلاث خطوات وهي التقييم, الاختيار والترتيب. تم اقتراح مقياسين للجوده لمساعده الخوارزم في عملية الاختيار والترتيب. المساحة, الطاقه المستهلكه والوقت اخذت في عين الاعتبار في عمليه تحسين تصميم الدوائر الكهربائيه. اختبرت الخوارزم المقترحه باستخدام مجموعه من الدوائر الكهربائيه القياسيه (SCAS'85) ودوائر كهربائيه اختيرت بطريقة عشوائية. كما تم مقارنة النتائج مع الطرق الاخرى المتواجده. نتائج الطريقة المقترحة اثبتت انها افضل من الطرق الاخرى.

مصطلحات البحث: التصميم الارتقائي للدوائر, تركيب المنطق, التطور المحاكى, المنطق المبهم, المشاكل المتعدّدة الأهداف

درجة الماجستير في العلوم الجامعة الملك فهد للبترول و معادن ظهران - المملكة العربية السعودية نوفمبر ٢٠٠٣

## Chapter 1

## INTRODUCTION

Logic circuits for digital systems may be combinational or sequential. A combinational circuit consists of logic gates whose outputs at any time are determined by combining the values of the applied inputs using logic operations. A combinational circuit performs an operation that can be specified logically by a set of Boolean expressions. In contrast, sequential circuits employ elements that store bit values. Sequential circuit outputs are function of the inputs and the bit values in the storage elements. These values, in turn, are a function of previously applied inputs and stored values. As a consequence, the outputs of a sequential circuit depend not only on the presently applied values of the inputs, but also on past inputs, and the behavior of the circuit must be specified by a sequence in time of inputs and internal stored bit values. This thesis deals with combinational logic circuits [36].

A combinational circuit consists of input variables, output variables, logic gates,

Figure 1.1: Block diagram of a combinational circuit.

and interconnections. The interconnected logic gates accept signals from the inputs and generate signals at the outputs. A block diagram of a combinational circuit is shown in Figure 1.1. The n input variables come from the environment of the circuit, and the m output variables are available for use by the environment. Each input and output variable exists physically as a binary signal that represents logic 1 or logic 0 [11].

For n input variables, there are  $2^n$  possible binary input combinations. For each binary combination of the input variables, there is one possible binary value on each output. Thus, a combinational circuit can be specified by a truth table that lists the output values for each combination of the input variables. A combinational circuit can also be described as a function of the n input variables.

## 1.1 Logic Design

Design of digital circuits requires knowledge of large collections of domain-specific rules. The process of implementing a digital circuit in hardware involves transforming the original logical specification into a form suitable for the target technology,

Figure 1.2: Conventional versus evolutionary design methodology.

optimizing the representation with respect to a number of user defined constraints (i.e., timing, fan-in/out, power, etc.), and finally carrying out technology mapping onto the target technology [28].

In designing complex systems, circuit designers usually have to tradeoff one design objective for another. For example, often a designer tries to find a possibly faster circuit compared to a given previously designed one. In seeking a faster circuit, one may end up having a complex system or a system that has higher power dissipation. The purpose of logic synthesis tools is to aid circuit designers in reaching an optimal tradeoff. Several logic synthesis algorithms are found in the literature [3, 4, 5, 6, 37].

Circuit designers use logic synthesis tools to create digital systems of arbitrary complexity. By using a top-down approach they tend to work in a space of lower dimensionality in which they are experts. However, this approach is somewhat constrained both by the training and experience of the designer and by the amount of domain-specific knowledge known to the designer. On the other hand, *iterative heuristics* may allow designers to define the search space of circuit design in a way

that is natural to both the problem and the implementation. These heuristics have tendency to search for a solution to the circuit design problem in a much larger, and often richer, design space beyond the realms of the traditional hardware design space. Heuristics can thus help explore the search space regions needed to reach designs that are beyond the scope of conventional methods. It may therefore be possible to use iterative heuristics to obtain novel designs that are difficult to discover by conventional heuristics. Figure 1.2 shows the difference between the conventional and the evolutionary methods for circuit design.

Furthermore, evolutionary design approaches do not assume a prior knowledge of any particular design domain. They can be used in domains where little knowledge is available or where such knowledge is costly to obtain. It is often possible to evolve hardware that is too complex in its structure and/or dynamics for human to design.

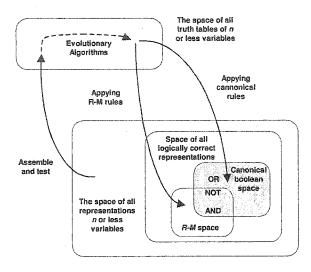

In conventional logic design, circuit designers begin with a precise specification in the form of truth tables or Boolean expressions. These expressions are manipulated by applying logic synthesis algorithms. The outcome of the logic synthesis algorithms will always be in the space of all logically correct representations as shown in Figure 1.3. On the contrary, the evolutionary algorithms work on a larger space that may not represent the desired function, but gradually pulls the specification of the circuit towards the target function.

It is well-known that many optimization problems arising in computer science, engineering, management, administration or other fields cannot be solved exactly

Figure 1.3: Evolutionary design process [28].

within reasonable time limits, at least not for problem sizes of practical interest. For this reason, heuristics have been introduced to find high quality solutions for these problems in reasonable time. Some heuristics are not restricted to specific problem types, but may be applied, with suitable modifications, to a broad class of optimization problems.

Heuristic algorithms, when properly exploited, will quickly enable the development of *acceptable* solutions. A heuristic algorithm will only search inside a subspace of the total search space for a *good* rather than the best solution which satisfies design constraints. Therefore, the time requirement of a heuristic is small compared to that of full enumerative algorithms.

It is possible to classify heuristics into iterative heuristics and constructive heuris-

tic. In constructive heuristics, a solution is generated from scratch by successive addition of certain elements or components, with or without backtracking (that is, removal of components that have been added at an earlier step). An example of constructive heuristics is the greedy heuristic [34]. On the other hand, iterative heuristics start with a complete feasible solution and refine this solution in order to improve the objective function value. One of the well known iterative heuristics is the local search algorithm. All modern iterative heuristics such as simulated annealing, tabu search, or genetic algorithms, are generalization of the local search heuristic. Readers are referred to [34] for a detailed description of these algorithms.

## 1.2 Problem Definition

The problem under consideration can be defined as follows:

Given the truth table of a function f and a target technology to work within, it is required to design an optimized combinational logic circuit that performs the function f subject to a set of constraints using Simulated Evolution Algorithm (SimE).

This problem is referred to as Evolutionary Logic Design through Simulated Evolution (SimE) algorithm.

### 1.3 Related Work

Evolutionary logic design has received increasing attention in the last decade. Motivated by de Garris's idea [10] back in 1993, Higuchi et al. [19] obtained an evolved circuit to solve the 6-multiplexer problem [24]. Later, in 1995, Thompson [38] managed to evolve a tone discriminator circuit using XC6200 FPGA. Thompson used the 1800-bits FPGA's configuration string as the *genotype* representation of the circuit. Thompson showed that Evolutionary Algorithms (EAs) can explore much richer design space [39]. Using EAs, he was able to produce circuits that are better than those produced by conventional methods in terms of number of gates.

Koza et al. employed genetic programming [23] and pioneered the evolution of analog circuits. Using a SPICE simulator, they automatically generated circuits which are competitive with those obtained using human designs and showed that it is possible to produce designs for quite complex analog circuits, namely: low-distortion op-amp, low-pass filter, and band-pass filters [22]. Genetic Programming is also used as intrinsic evolution of analog circuits [49]. A functional level evolution was proposed by Higuchi [18]. A complete review and taxonomy of the field is described in [14, 46, 32].

In a recent development, much attention is given to the evolutionary design of arithmetic circuits as they provide the essential building blocks needed for larger DSP applications. Such effort has resulted in the development of arithmetic circuits that range from a simple sequential adder structure to the more complex 3-bit multiplier design. Fogarty and Miller build some arithmetic circuits that cannot be produced by human designer's conventional methods [15, 27]. Both of these used Genetic Algorithms. Miller improved his findings by using Evolutionary Strategies to evolve arithmetic circuits [28]. Coello et al. proposed a similar approach to evolve a circuit using Genetic Algorithm (GA) [7, 8].

## 1.4 Motivation

Design is usually considered to be an activity requiring considerable human creativity and knowledge. Even the definition of the term *design* itself is quite elusive, since it can be interpreted in several different ways depending on the task to be performed.

The definition of design that fulfills the purposes of our thesis is the process of deriving, from a specified input/output behavior, a structure (in our case a certain combination of logic gates) that is functional (produces all the outputs desired for all the inputs specified) satisfying a set of objectives.

Furthermore, we want this design to be optimum in terms of certain structural features (e.g., the number of gates used). The design process is a tedious and error prone task that usually requires considerable human expertise.

Several techniques in evolutionary design of digital circuits have been studied.

Most of the work being done in evolutionary logic synthesis is just random search where the evolutionary algorithm blindly evolves a circuit satisfying a given set of objectives without using the rules and techniques used in conventional logic synthesis. It is believed that incorporating logic synthesis rules and guidelines combined with the idea of assemble-and-test could lead to better results.

The motivation of our thesis is to develop a computer-based tool that can make the design process less tedious for the human designer without sacrificing quality of the designs produced. In this thesis, we limit our focus to combinational logic circuits, which contains no memory elements and no feedback paths. The use of Simulated Evolution algorithm is considered.

Simulated Evolution (SimE) algorithm showed better result in most of the other optimization problems when compared to other evolutionary algorithm [34]. This is due to the nature of the algorithm and its converging aspects. Also, SimE uses only one solution (chromosome) resulting in less memory requirement. Moreover, SimE algorithm uses goodness measure to guide the algorithm in the search space. The more knowledge about the problem incorporated into the goodness measure, the better the performance of SimE algorithm in terms of CPU time and quality of solution. Therefore, using the Simulated Evolution algorithm as our evolutionary algorithm should provide a good solution for the required automated synthesis tool.

## 1.5 Thesis Organization

This thesis is organized as follows. In Chapter 2, some basic background material about conventional logic design (CLD) and logic design optimization is introduced. In Chapter 3, evolutionary logic design (ELD) is presented. Detailed discussion on Simulated Evolution Algorithm (SimE) is presented in Chapter 4. In Chapters 5 and 6, the proposed implementation of the Simulated Evolution Algorithm (SimE) for Logic Design is presented and the proposed goodness measures are explained. Experimental results of the proposed techniques is given in Chapter 7. Comparison with Tabu Search (TS), Genetic Algorithm (GA) [7], Ant Colony Algorithm (ACO) [9] and SIS [37] are given in Chapter 8. Finally, the thesis ends by some conclusions and future directions in Chapter 9.

## Chapter 2

## **BACKGROUND**

This chapter provides some necessary background information. The first section discusses the conventional logic design techniques and definitions. Next, logic design optimization is presented and the difference between optimization for objectives or using constraint optimization is explained. This is followed by a section on multi-objective optimization. Following this, fuzzy logic for multi-objectives optimization is presented.

## 2.1 Conventional Logic Design (CLD)

The dramatic increase in designer productivity over the past decade in the area of VLSI circuit design is a direct result of the development of sophisticated computer-aided design tools. Logic synthesis techniques speed up the design cycle and reduce

the human effort. Synthesis algorithms work on a model of the circuit, not the circuit itself. Circuit representation is therefore important to understand. Reader should refer to any logic design book such as [26] for more elaborate background material.

Logic synthesis area is usually divided into two-level synthesis (PLA) and multilevel synthesis. Because of the architecture inherent to PLAs, optimization methods focus almost exclusively on minimizing the number of PLA product terms, which in turn minimizes the PLA area. The area of two-level combinational logic minimization has already matured. One can routinely find a minimum or near-minimum sum-of-product form for a logic function. These functions can be multiple output, incompletely specified, and functions with multiple-valued input variables. Functions with hundreds of inputs and outputs are within the realm of the algorithms. The optimization can also be done in a reasonable amount of computing time [5].

The other method for implementing logic is multilevel logic. Because of the increased potential for reusing sublogic, there are more degrees of freedom in the solution representation than in the PLA case. Consequently, it has been much more difficult to synthesize this type of logic using manual synthesis. In the following subsection, a survey of the existing conventional logic synthesis methodologies is given.

#### 2.1.1 Two-level Boolean Functions

Logic function can be represented in a variety of ways. One can use a two-level representation in which literals are combined with a single operator (AND operator) and then these terms are combined with a second operator (OR operator) which is SOP form. When a logic function is expressed in terms of product terms, which involve all input variables and all true output products are present, the expression is referred to as a canonical Boolean expression. Usually the goal of logic synthesis is to represent a logic function in the simplest way by reducing the number of product terms and literals [28].

#### 2.1.2 Multilevel Boolean Functions

The two-level logic provides the minimum logic required to implement any arbitrary Boolean function. However, there exist some Boolean functions that are very inefficiently represented in two-level logic. On the contrary, multilevel logic representation of a logic function allows the use of factoring and decomposition into sub-functions. Consider, for example, the following logic function.

$$F = a \cdot e + a \cdot f + b \cdot c \cdot e + b \cdot c \cdot f + b \cdot d \cdot e + b \cdot d \cdot f$$

The function can also be expressed as follows:

Figure 2.1: Representation of a boolean function in (a) in two-level logic (b) in multi-level logic.

$$F = (a + b \cdot (c + d)) \cdot (e + f)$$

It is easy to notice that the first representation of the function f has 16 literals, while the second has only 6. Thus, the multilevel logic representation will reduce the area requirement of a Boolean function, as shown in Figure 2.1.

The starting point for multilevel minimization is the minimum two-level canonical form. Sophisticated heuristic-based minimization algorithms have been written which try to reduce the literal counts in Boolean multilevel expressions [5, 6, 28].

#### 2.1.3 Reed-Muller and Exclusive-OR Logic

It is well known that many Boolean functions which can be easily implemented using XOR gates are very inefficiently represented in canonical Boolean logic. The most extreme case of this being the n-bit parity functions which can be realized with n-1 XOR gates but if AND-OR logic is used, it requires  $2^{n-1}-1$  OR gates and a large number of AND gates. When a Boolean logic function is expressed using XOR gates and uncomplemented variables it is called a *Reed-Muller* (RM) canonical form [16]. If any particular variable is allowed to be complemented or uncomplemented throughout the expansion then the representation is known as a *fixed polarity RM form*. Finding a good polarity is a difficult problem and evolutionary algorithm have been used for this purpose. Work has been done on minimizing the less restricted XOR sum-of-products representation [38].

## 2.2 Logic Design Optimization

Logic circuit optimization is often performed in conjunction with synthesis. Optimization is motivated not only by the desire of maximizing the circuit quality, but also by the fact that synthesis without optimization would yield noncompetitive circuits, and therefore its value would be marginal. In this thesis, the optimization objectives considered are area, power and delay [2, 13, 26]

Circuit area is measured by the sum of the areas of the circuit components and

therefore it can be computed from a structural view of a circuit, once the areas of the components are known. The area computation can be performed hierarchically. Usually, the fundamental components of digital circuits are logic gates and registers, whose area is known *a priori*. The wiring area has a minor effect and can be neglected [25, 26, 31].

However, circuit power and delay are not additive, and therefore computation for power and delay as objectives require analyzing the structure and often the behavior of the circuit. Often simplifying assumptions for the computations of power consumption and timing (delay) are made assuming that all inputs are available at the same time. Also, another simplifying assumption is to use a model for the power and delay measurements. These model can simplify the computation of the power and delay at the expense of accuracy. For timing performance, the delay of the most critical path of the circuit is considered. More details on area, power and delay computations are given later.

# 2.3 Multi-objective Optimization

Multi-objective optimization (also called multi-criteria optimization, multi-performance or vector optimization) can be defined as the problem of finding a vector of decision variables which satisfies constraints and optimizes a vector function whose elements represent the objective functions. These functions form a mathematical description

of performance criteria which are usually in conflict with each other. Formally, we can state the general multi-objective optimization problem (MOP) as follows:

**Definition 1 (General MOP):** Find the vector  $\vec{x}^* = [x_1^*, x_2^*, ..., x_n^*]^T$  which will satisfy the m inequality constraints:

$$g_i(\vec{x}) \ge 0 \ i = 1, 2, ..., m$$

(2.1)

the p equality constraints

$$h_i(\vec{x}) = 0 \ i = 1, 2, ..., p$$

(2.2)

and optimizes the vector function

$$\vec{f}(\vec{x}) = [f_1(\vec{x}), f_2(\vec{x}), ..., f_k(\vec{x})]^T$$

(2.3)

where  $\vec{x}^* = \left[x_1^*, x_2^*, ..., x_n^*\right]^T$  is the vector of decision variables.

In other words, we wish to determine from among the set F of all numbers which satisfy 2.1 and 2.2 the particular set  $x_1^*, x_2^*, ..., x_n^*$  which yields the optimum values of all the k objectives of the problem [26].

The idea of using multi-objective optimization techniques to handle constraints is not new. Some researchers have proposed to redefine the single-objective optimization of  $f(\vec{x})$  as a multi-objective optimization problem in which we will have m+1 objectives, where m is the number of constraints. Then, we can apply any multi-objective optimization technique to the new vector  $\vec{v} = (f(\vec{x}), f_1(\vec{x}), ..., f_m(\vec{x}))$ , where  $f_1(\vec{x}), ..., f_m(\vec{x})$  are the original constraints of the problem. An ideal solution

$\vec{x}$  would thus have  $f_i(\vec{x}) = 0$  for  $1 \le i \le m$  and  $f(\vec{x}) \le f(\vec{y})$  for all feasible  $\vec{y}$  (assuming minimization) [8, 40, 41, 42]. In many cases, it is not clear how one can balance different objectives by a weight function especially when the various objectives are defined over different domains. Also, it is not always possible to have a crisp ranking of the individual objectives. Another difficulty is that the outcome of such ranking is not always predictable especially when some of the criteria are correlated. Fuzzy logic provides a convenient framework for solving this problem. It allows one to map values of different criteria into linguistic values, which characterize the level of satisfaction of the designer with the numerical values of objectives. Each linguistic value is then defined by a membership function which maps numerical values of the corresponding objective criterion into the interval [0, 1]. The desires of the decision maker are conveniently expressed in terms of fuzzy logic rules and fuzzy preference rules. The executing/firing of such rules produces numerical values that are used to decide a solution goodness. In practice, this approach has been proven very powerful for finding compromise solutions in different areas of science and engineering [34].

# 2.4 Fuzzy Logic

Fuzzy logic deals with approximate rather than precise modes of reasoning. Therefore, fuzzy logic is capable of handling the uncertainty of data. Also, natural language, which is the basis of fuzzy logic, is more convenient for expressing engineering problems. In general, fuzzy logic can be viewed as a nonlinear mapping of an input data vector into a scalar output. However, the flexibility of fuzzy logic may create lots of different mappings for a single problem instance. Therefore, a good understanding of the fuzzy set theory, fuzzy reasoning and fuzzy rules is needed.

# 2.4.1 Fuzzy Set Theory

An element in fuzzy logic may partially belong to a fuzzy set by a certain degree compared to classical (crisp) set in which each element can either belong to the set or not.

A fuzzy set A of universe of discourse X is defined as  $A = \{(x, \mu_A(x)) \mid all \ x \in X\}$ , where X is a space point and  $\mu_A(x)$  is a membership function of x being an element of A. A membership function  $\mu_A(x)$  is a mapping of x in A that maps X to the membership space M. The range of the membership function is a subset of the non-negative real numbers whose boundaries are finite [50]. Elements with zero degree of membership are normally not listed.

#### Fuzzy Reasoning

Unlike classical reasoning in which propositions are whether true of false, fuzzy logic establishes approximate truth value of propositions based on linguistic variables and inference rules [47]. A linguistic variable is a variable whose values are words or sentences in natural or artificial language. It is concerned with the use of fuzzy

values that captures the meaning of words, human reasoning and decision-making. An example of linguistic variable is circuit's area. This variable can be expressed by linguistic values like very small, small, average, large and very large circuit, rather than  $20 \ \mu m^2$ ,  $30 \ \mu m^2$ ,  $50 \ \mu m^2$ ,  $75 \ \mu m^2$ , and  $100 \ \mu m^2$ .

A linguistic variable carries the concept of fuzzy set qualifiers, called *hedges*. Hedges are terms that modify the shape of fuzzy sets. They include adverbs such as very, somewhat, quite, more or less, and slightly. They are used as modifiers, truth-values, probabilities, quantifiers and/or possibilities of a certain linguistic variable.

Formally, a linguistic variable comprises of five elements [48]:

- 1. The variable name

- 2. The primary term set

- 3. The universe of discourse U

- 4. A set of syntactical rules that allows composition of the primary terms and hedges to generate the term set

- 5. A set of semantic rules that assigns each element in the set a linguistic meaning.

#### **Fuzzy Operators**

There are two basic types of fuzzy operators. The operators for the intersection, interpreted as the logical "and", and the operators for the union, interpreted as the

logical "or" of fuzzy sets. The intersection operators are known as triangular norms (t-norms), and union operator as triangular co-norms (t-co-norms or s-norms) [50]. Some examples of s-norm operators are given below, (where A and B are the fuzzy sets of universe of discourse X).

- 1. Maximum.  $[\mu_{A[]B}(x) = max\{\mu_A(x), \mu_B(x)\}].$

- 2. Algebric sum.  $[\mu_{A|A}(x) = \mu_A(x) + \mu_B(x) \mu_A(x)\mu_B(x)].$

- 3. Bounded sum.  $[\mu_{A \cup B}(x) = min(1, \mu_A(x) + \mu_B(x))].$

- 4. Drastic sum.  $[\mu_{A \bigcup B}(x) = \mu_{A}(x) \text{ if } \mu_{B}(x) = 0, \quad \mu_{B}(x) \text{ if } \mu_{A}(x) = 0, \quad 1 \text{ if } \mu_{A}(x), \mu_{B}(x) > 0].$

An s-norm operator satisfies commutativity, monotonicity, associativity and  $\mu_{A\bigcup 0}(x) = \mu_A(x)$  properties.

Following are some examples of t-norm operators.

- 1. Minimum.  $[\mu_{A \cap B}(x) = min\{\mu_{A}(x), \mu_{B}(x)\}].$

- 2. Algebraic product.  $[\mu_{A \cap B}(x) = \mu_A(x)\mu_B(x)]$ .

- 3. Bounded product.  $[\mu_{A \cap B}(x) = max(0, \mu_A(x) + \mu_B(x) 1)].$

- 4. Drastic product.  $[\mu_{A \cap B}(x) = \mu_{A}(x) \text{ if } \mu_{B}(x) = 1, \quad \mu_{B}(x) \text{ if } \mu_{A}(x) = 1, \quad 0 \text{ if } \mu_{A}(x), \mu_{B}(x) < 1].$

Like s-norm, t-norms also satisfy commutativity, monotonicity, associativity and  $\mu_{A \cap 1}(x) = \mu_A(x)$ . Also, the fuzzy complementation operator is defined as follows.

$$\bar{\mu}_B(x) = 1 - \mu_B(x)$$

(2.4)

## 2.4.2 Multi-objective Optimization Using Fuzzy Logic

Approximate reasoning can be made based on linguistic variables and their values. Rules can be generated based on previous experience. The rules are expressed as If ... Then statements. Connectives such as AND and OR can be used in approximate reasoning to join two or more linguistic values. The If part (antecedent) is a fuzzy predicate defined in terms of linguistic values and fuzzy operators (AND and OR). The Then part is called the consequent.

In optimization problems, the linguistic value used in the consequent part identifies the fuzzy subset of good solutions. Therefore, the result of evaluation of the antecedent part identifies the degree of membership in the fuzzy subset of good solutions according to the fuzzy rule in question. If more than one rule is used to perform decision-making, each rule can be evaluated to generate a numerical value. Then, these numerical values from various evaluations of different rules can be combined to generate a crisp value on a higher level of hierarchy.

Consider the circuit design problem with minimization of area, delay, and power consumption. Three linguistic variables area, delay and power introduced. Then

good solutions can be characterized by the following fuzzy rule.

If the circuit has (small area) and (less delay) and (less power consumption) then it is a good solution.

In the traditional fuzzy logic, the minmax operators are used to build the above fuzzy rule. However, it was shown in [45] that these operators can lead to undesirable behavior. This behavior has led to the development of other fuzzy operators such as the *Ordered Weighted Averaging (OWA)* operator explained below.

#### Ordered Weighted Averaging (OWA) Operator

Generally, the formulation of multi criterion decision functions neither desires the pure "AND-ing" of t-norm nor the pure "OR-ing" of s-norm. The reason for this is the complete lack of compensation of t-norm for any partial fulfillment and complete submission of s-norm to fulfillment of any criteria. Also the indifference to the individual criterion of each of these two forms of operators led to the development of Ordered Weighted Averaging (OWA) operators [43, 44]. This operator allows easy adjustment of the degree of "AND-ing" and "OR-ing" embedded in the aggregation. According to [43, 44], "OR-like" and "AND-like" OWA for two fuzzy sets A and B are implemented as given in Equations 2.5 and 2.6 respectively.

$$\mu_{A \cup B}(x) = \beta \times \max(\mu_A, \mu_B) + (1 - \beta) \times \frac{1}{2}(\mu_A + \mu_B)$$

(2.5)

$$\mu_{A \cap B}(x) = \beta \times \min(\mu_A, \mu_B) + (1 - \beta) \times \frac{1}{2}(\mu_A + \mu_B)$$

(2.6)

where  $\beta$  is a constant parameter in the range [0,1]. It represents the degree to which OWA operator resembles a pure "OR" or pure "AND" respectively.

# 2.5 Concluding Remarks

In this chapter, some basic background information were reviewed including the conventional logic design (CLD) and logic design optimization. Then, multi-objectives optimization was presented. Also, fuzzy logic and multi-objectives optimization using fuzzy logic were discussed.

# Chapter 3

# **EVOLUTIONARY LOGIC**

# DESIGN (ELD)

Evolutionary logic design considers a new concept for automatic design of digital systems: instead of using human conceived models, abstractions, and techniques, it employs search algorithms to develop good designs. This idea is summarized in Thompson [38]:

Imagine a design space where each point in that space represents the design of a digital circuit. All possible digital circuits are there, given the component types available to electronics engineer, and the technological restrictions on how many components there can be and how they can interact. In this metaphor, we loosely visualize the circuits to be arranged in the design space so that 'similar' circuits are close to each

other.

Evolutionary logic design deals with a huge search space, requiring, therefore, powerful search techniques to handle the task. Naturally, when the search space is very large, random search has little chance to succeed. Hence, this new approach to circuit design does not resume choosing a design problem and applying a search techniques. Instead, some procedures have to be followed:

- The search space sampled by the algorithm must have its size limited. Although it is important to allow the sampling of a wide variety of topologies, some criteria should be chosen to control the number of possible solutions.

- It is usually necessary to adapt the search techniques to the particularities of the design problem.

The search space size is a very subtle issue: it should be large enough to include a good variety of novel circuit topologies; nevertheless, if the design space increases without restriction, the chances to find a good solution are very small. This is a very important issue for the search techniques applied in this thesis. These algorithms suit well to sample large design spaces, performing better than standard optimization techniques. Nonetheless, for very large search spaces, even evolutionary algorithms have their limitations.

Another important issue is the inclusion of special techniques into the search tool in order to successfully find a circuit that conforms with all specifications such as the inclusion of some kind of previous knowledge on the circuit design.

After this discussion one may think: Why would we be interested in using search algorithms to perform logic design? Is not the size of the search space to be sampled a drawback that we would not have to face using conventional techniques? The following points will summarize the answer to this question:

- Potential to find novel circuits.

- The possibility to find new design rules from the novel circuits obtained.

- Evolutionary methods can contemplate a larger set of design specifications compared to human design techniques (area, delay, power).

- Evolutionary systems have been able to achieve competitive circuits when compared with the state of the art in electronics.

- The constant increase in the microprocessors' speed will partially alleviate the drawback of the design space size.

In this chapter, a brief description about evolutionary algorithms will given.

Then, the concept of assemble and test and exploring the search space will be discussed. A survey on the work being done on evolutionary logic design and some observations on them will be presented.

# 3.1 Genetic Algorithm

Genetic algorithm operates on a population (or set) of individual(s) (or solution(s)) encoded as strings or matrices. These strings represent points in the search space. In each iteration, referred to as a generation, a new set of strings that represent solution(s) (called offsprings) is created by using some evolutionary operation such as mutation or crossover on the current generation. The encoding of the strings or matrices (chromosomes) is a very critical aspect for the efficiency of the algorithm. Therefore, an efficient encoding of digital circuits into chromosomes is important for the evolutionary logic design techniques. In the case of genetic algorithms, encoding represents the genotype-phenotype mapping between the circuit and the chromosomes. In order to preserve the validity of the circuit being evolved due to the evolution process, some constraints need to be set on the chromosome encoding.

In addition to the chromosome encoding, each chromosome is associated with a fitness value (cost function) to evaluate the goodness (quality) of the solution. The fittest the chromosome, the greater chance a chromosome will survive in the following generation. Therefore, the choice of the fitness (cost) function will affect the behavior of the evolutionary algorithm in the quality of the solution being produced.

The evolution process starts by creating an initial population. This initial population can be random or constructive, depending on the objective of the design.

Miller et al. initialized the population with the chromosome of a given circuit and

its mutated copies [42]. The objective was to focus the evolution process on finding more efficient circuits. It is however noticed that many researchers prefer random initialization since it allows exploring more regions in the design space.

# 3.2 Exploring the Space of all Representations

The survivability of an organism can be seen as a process of assembling a larger system from a number of component parts and then testing the organism in the environment in which it finds itself (assemble-and-test). Figure 3.1 illustrates this concept in the general space of designs. The top-down rule-based space of designs is shown in gray as a small sub-region in the much larger space of all possible designs. Occasionally by a process of human inspiration or accidental discovery this space is widened as new concepts and principles are developed. Generally speaking, restrictive assumptions have to be made about the range of parts which can be used within this space. This is imposed by the constraints of a tractable system of rules. On the other hand, it is argued here that by employing the simple idea of assemble-and-test together with an evolutionary algorithm one can explore the entire design space and use a much larger collection of parts precisely because of the absence of imposed rules of design [28].

The concept of assemble-and-test together with an evolutionary algorithm to gradually improve the quality of a design has largely been adopted in the field of

Figure 3.1: Conventional design versus evolutionary design with assemble-and-test.

Evolvable Hardware where the task is to build an electronic circuit. These electronic circuits are encoded in a chromosome. The complete set of chromosomes is called a genotype. The resulting circuit which can be constructed from a chromosome or genotype is called phenotypes. Research in Evolvable Hardware can be sub-divided into two main categories: intrinsic evolution and extrinsic evolution. The former refers to an evolutionary process in which each phenotype is built in electronic hardware and tested. The latter uses a model of the hardware and thus evaluates the phenotypes in software. Each of these categories can be further sub-divided into analogue or digital domains. Intrinsic evolution in the analogue domain has recently become possible because of the availability of reconfigurable analogue devices. In the introduction, it was shown how the use of an evolutionary algorithm combined with assemble-and-test could be used to explore a much larger area of design space

Figure 3.2: How "assemble-and-test" reaches the unknown regions of the space of all representations.

than using a top-down rule based design algorithm. Figure 3.2 shows a particular case of this for the problem of finding efficient representations of Boolean functions and it illustrates one of the fundamental concepts of this proposal. In conventional logic design one begins with a precise specification in the form of a truth table, binary decision diagram, symbolic expression etc. The expression is manipulated by applying canonical Boolean rules or Reed-Muller algebraic rules. One never escapes from the space of logically correct representations. The methods though powerful in that they can handle large numbers of input variables, yet they are not adaptable to new logical building blocks and require a great deal of analytical work to produce small optimizations in the representation. Assembling a function from a number of component parts begins in the space of all representations and maps it into the space of all the truth tables with m input variables ( $m \le n$ ). The evolutionary algorithm

then gradually pulls the specification of the circuit towards the target truth table (shown as a small shaded box). Thus the algorithm works in a much larger space of functions many of which do not represent the desired function.

# 3.3 Survey on Evolutionary Logic Design (ELD)

In the following subsections, the previous work on the evolutionary logic synthesis will be addressed in two aspects: the circuit encoding and the cost function.

# 3.3.1 The Circuit Encoding

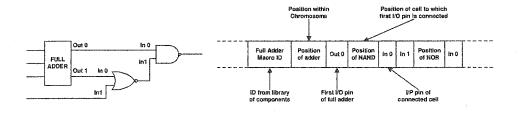

A fixed length chromosome for circuit representation is used by Hounsell [20]. The first part of the chromosome is used for describing the inputs of the circuit while the last part is used for describing the outputs of the circuit. The position of each logic element is referenced within the chromosome. Figure 3.3 displays the relative location of each encoded section. Within the chromosome, a specific location is allocated for each logic element in the circuit. Interconnection between cells is not restricted to its nearest positional neighbor. Also, cells are free to connect to other cells at higher position within the chromosome. Feedback connections are not permitted. Figure 3.4 demonstrates the encoding of a macro block (full-adder) with its connectivity within the chromosome.

Another representation made by Miller who suggested that the chromosome rep-

Figure 3.3: Chromosome representation in Hounsell [20].

Figure 3.4: Macro blocks and its genotype representation in Hounsell [20].

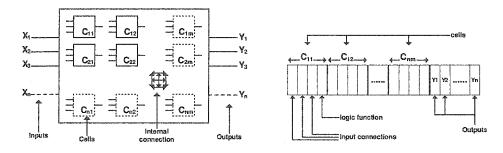

resentation should match the hardware's geometry configuration [29]. A matrix of  $n \times m$  array of logic cells is used as the phenotype representation in the case of FPGA. The interconnections together with gate level functionality for the cells are defined by the genotype (chromosome). This genotype-phenotype mapping is shown in Figure 3.5.

Figure 3.5: Chromosome representation in Miller [28, 29].

Any function that can be realized by an FPGA can be assigned to any gene of

Table 3.1: Possible cell functions in Miller [28, 29].

| Alphabet | Function               | Alphabet | Function                                    |

|----------|------------------------|----------|---------------------------------------------|

| 0        | 0                      | 10       | $a\oplus b$                                 |

| 1        | 1                      | 11       | $a\oplus b$                                 |

| 2        | a                      | 12       | a+b                                         |

| 3        | b                      | 13       | $a + \overline{b}$                          |

| 4        | ā                      | 14       | $\bar{a} + b$                               |

| 5        | $\bar{b}$              | 15       | $\bar{a} + \bar{b}$                         |

| 6        | $a \cdot b$            | 16       | $a \cdot \bar{c} + b \cdot c$               |

| 7        | $a \cdot \overline{b}$ | 17       | $a\cdot \overline{c} + \overline{b}\cdot c$ |

| 8        | $ar{a}\cdot b$         | 18       | $\bar{a}\cdot\bar{c}+b\cdot c$              |

| 9        | $ar{a}\cdot ar{b}$     | 19       | $\bar{a}\cdot\bar{c}+\bar{b}\cdot c$        |

the chromosome. Table 3.1 lists all the possible functions.

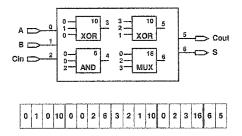

Each gene is a sequence of integers representing the target interconnection of gate's inputs and the gate type. Consider, for example, the case shown in Figure 3.6. The first quadruplet of the chromosome is 0-1-0-10, which means that the first input of the cell is connected to pin number 0, the second input to pin number 1, and the third input to pin number 0 respectively. The gate type is 10, which is a two input XOR (the third input is not used). The interconnection between cells is restricted by the *levels-back parameter*, which denotes the number of previous column in the array that a cell can be connected to. If the levels-back parameter is one, then each cell must be connected to its immediate neighbor in the previous column. Cells within any particular column cannot be connected together, and feedback connections are not allowed.

The third representation by Coello et al. [7, 8], used the same chromosome representation of circuits as those by Miller [28, 29]. However, the organization of the

Figure 3.6: Example of genotype-phenotype mapping in Miller [28, 29].

Figure 3.7: Representation of gene in chromosome in Coello [7, 8].

chromosome is different. Each cell is a gate of the type of AND, NOT, OR, XOR or WIRE. Each of them is encoded in a triplet of inputs and gate type, as illustrated in Figure 3.7.

Miller represented each cell as different integers [28, 29]. This approach is impractical for large circuit. On the other hand, Coello et al. represented a gate at position (i, j) can only be connected to the one at ((i - 1), j) [7, 8]. This restriction reduces the cardinality of alphabet needed to represent the chromosome, since the integer number to represent each cell increases only column wise.

#### 3.3.2 The Cost Function

The cost function (fitness) used by Hounsell is represented by a percentage of circuit functionality generated by the evolutionary algorithm [20]. Correctness is calculated by summing the total number of correct bits produced by the circuit solution under evaluation and comparing this to the desired output response. Fitness is expressed

mathematically as follows:

$$R_b = 2^I \times O$$

$$Fitness = E_b/R_b$$

Where  $R_b$  is the total number of bits comprising the desired output vectors,  $E_b$  is the actual number of bits matched with the desired output vectors during evaluation, O is the number of output pins and I is the number of input pins. Evaluation of the circuit (solution) is achieved through interaction with a HDL (Hardware Description Language).

Since all functions are specified by a truth table, Miller's cost function (fitness) of a genotype is based on the number of correct output bits specified by the truth table [29, 28]. For a one-bit adder with carry, there are 8 input cases and 2 outputs, this results in 16 output bits. A fully correct circuit would have fitness 16.

Colleo's cost function (fitness) evaluation works in two stages. At the beginning of the search, only validity of the circuit outputs is taken into account [7, 8]. Once a functional solution appears, then the fitness function is modified such that any valid designs produced are rewarded for each WIRE gate that they include, so that the algorithm tries to find a correctly functional circuit with the maximum number of WIREs.

# 3.4 Observations

It is interesting to note that non-deterministic iterative heuristics tend to favor the use of XOR gates, since this gate allows producing, in many cases, solutions with a shorter symbolic representation. These solutions, are however not entirely obvious for human designers. Iterative heuristics tend to use multi-level XORs gates to produce the same effect as that a human designer would achieve using a combination of logic gates.

Although it has been shown that iterative heuristics can in fact produce fully functional circuits, or even efficient ones (in terms of the number of logic gates used), there is some concern about the process of producing a circuit. We have seen that in the evolutionary design approach, one considers the problem of designing a circuit as building a black box whose inputs and outputs are the inputs and outputs of the desired circuit. The details of the circuit itself are encoded in the form of a chromosome. Evolutionary algorithms will then blindly evolve circuits according to a given set of objectives.

Another point to consider is redundancy in the evolving circuit. It has been shown that some forms of redundancy could be useful for the evolution process [17]. However, if the genotype representation and genetic operators are not well implemented, we may end up with circuits having many redundancies. This redundancy may in turn spoil the evolution, making iterative heuristics to explore regions where

there are no acceptable solutions at all.

Some of the key points observed after studying the above mentioned approaches are summarized below.

- 1. Instead of blindly evolving a circuit, we need some procedures to guide the evolution process. These procedures should help iterative heuristics to find an optimal solution. We believe that integrating some rules in logic synthesis is the answer to this problem. These can be used to direct the search. One easy example of these rules is putting an inverter at the output of (sub-)circuit built to toggle the fitness of the current solution.

- 2. We can view the problem of circuit design as a problem of assembling logic blocks to implement a desired functionality. Almost similar to the growing circuits approach used by Miller [30], we shall constructively build a circuit by assembling all the required logic and/or sub-functions through the evolution process.

# 3.5 Concluding Remarks

In this chapter, we have introduced evolutionary logic design in the first section followed by some discussion on evolutionary algorithms. Then, a survey on pervious work in evolutionary logic design has been presented. This is followed by some observations on these implementations.

# Chapter 4

# SIMULATED EVOLUTION

# (SIME) ALGORITHM

Simulated Evolution (SimE) which was proposed by Kling and Banerjee in 1987 is based on an analogy with the principles of natural selection thought to be followed by various species in their biological environments [21]. During the process of biological evolution, organisms tend to develop features that allow them to adapt to the peculiarities of their environment. The more an organism adapts to its environment, the better are its chances of survival. In other words, by adapting, an organism optimizes its chances of surviving in its environment. Hence, adaptation is seen as a form of optimization. This similarity has given rise to a new class of randomized iterative algorithms which consists of Genetic Algorithms, Simulated Evolution, and Stochastic Evolution. All three algorithms of this class

are general randomized search heuristics that are based on concepts learned from biological evolution. For all three algorithms, the cost function is an estimation of the degree of adaption of a particular solution to the target objective. For a maximization problem, the higher the value of the objective function is, the more that particular solution is adapted to its environment. Simulated Evolution will be the subject of this chapter [21, 34].

In this chapter, SimE algorithm is introduced. Also, a detailed analysis of the SimE algorithm and operators are addressed afterward. This is followed by a qualitative comparison of SimE and Genetic Algorithm (GA).

# 4.1 SimE Algorithm: Evaluation, Selection and Allocation

Combinatorial optimization problems seek to find a global optimum of some real valued cost functions  $cost: \Omega \to \mathbb{R}$  defined over a discrete set  $\Omega$ . The Set  $\Omega$  is called the state space and its elements are referred to as states. A state space  $\Omega$  together with an underlying neighborhood structure (the way one state can be reached from another state) form the solution space.

The Simulated Evolution (SimE) algorithm is a general search strategy for solving a variety of combinatorial optimization problems [21]. The SimE algorithm starts from an initial assignment, and then, following an evolution-based approach,

it seeks to reach better assignments from one generation to the next. SimE assumes that there exists a population P of a set M of k elements. In addition, there is a cost function Cost that is used to associate with each assignment of an element m a cost  $C_m$ . The cost  $C_m$  is used to compute the goodness (fitness)  $g_m$  of element m, for each  $m \in M$ . Furthermore, there are usually additional constraints that must be satisfied by the population as a whole or by particular elements. A general outline of the SimE algorithm is given in Figure 4.1.

SimE algorithm proceeds as follows. Initially, a population<sup>1</sup> is created at random from all populations satisfying the environmental constraints of the problem. The algorithm has one main loop consisting of three basic steps, *Evaluation*, *Selection*, and *Allocation*. The three steps are executed in sequence until the population average *goodness* reaches a maximum value, or no noticeable improvement to the population *goodness* is observed after a number of iterations. Another possible stopping criterion could be to run the algorithm for a prefixed number of iterations (see Figure 4.1).

Combinatorial optimization problems can be modeled in a number of ways. A generic formulation is the following: Given a finite set M of distinct movable elements and a finite set L of locations, a state is defined as an assignment function  $S: M \to L$  satisfying certain constraints.

<sup>&</sup>lt;sup>1</sup>In SimE terminology, a population refers to a single solution. Individuals of the population are components of the solution; they are the movable elements.

```

ALGORITHM Simulated_Evolution(E, ,L, Stopping-Criteria);

INITIALIZATION;

Repeat

EVALUATION:

For Each m \in M Do g_m = \frac{O_m}{C_m} End For Each;

SELECTION:

For Each m \in M Do

If Random \leq Min(1 - g_m + B; 1)

Then P_s = P_s \cup \{m\};

Else P_r = P_r \cup \{m\};

EndIf;

EndForEach;

Sort the elements of P_s;

ALLOCATION:

For Each m \in P_s Do F_a(m) End For Each;

Until Stopping-criteria are met;

Return (BestSolution);

End Simulated_Evolution.

```

Figure 4.1: Simulated Evolution algorithm [21, 34].

Many of the combinatorial problems can be formulated according to this generic model. Below is an example on Quadratic Assignment Problem (QAP):

# Example 1 Quadratic Assignment Problem(QAP)

**Problem:** Given a set M of n modules and a set L of |L| locations.  $|L| \ge n$ . Let  $c_{i,j}$  be the number of connections between elements i and j, and  $d_{k,l}$  be the distance between locations k and l.

**Objective:** Assign each module to a distinct location so as to minimize the wire length needed to interconnect the modules. To formulate QAP in terms of the above state model, choose  $M = \{1, 2, ..., |M|\}$  and

Figure 4.2: Evaluation.

$L=\{1,2,\ldots, \mid L\mid\}$ . Then a state is defined as the *onto function*  $S: M=\{1,\ 2,\ \ldots,\ \mid M\mid\} \ \to \{1,\ 2,\ \ldots,\ \mid L\mid\}$ . In this case, one additional constraint is required, which can be stated as  $S(i)\neq S(j) \ \forall \ i\neq j$ , i.e., no two elements are assigned to the same location.

The cost of a state, Cost(S) is the wire length required to interconnect all the elements in their present locations. That is,

$$Cost(S) = \sum_{i=1}^{n} \sum_{j=1}^{n} c_{i,j} d_{S(i),S(j)}$$

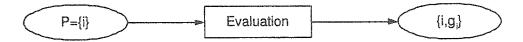

### 4.1.1 Evaluation

The Evaluation step consists of evaluating the goodness of each individual i of the population P (see Figure 4.2). The goodness measure must be a single number expressible in the range [0,1]. Goodness is defined as follows:

$$q_i = O_i/C_i$$

where  $O_i$  is an estimate of the optimal cost of individual i, and  $C_i$  is the actual cost of i in its current location.

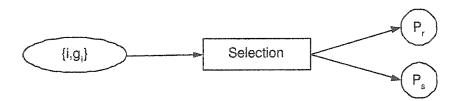

Figure 4.3: Selection.

```

Function Selection(m, B);

/* m: is a particular movable element; */

/* B: Selection bias;*/