# **Experiment 8: Microcontroller on an FPGA**

# **Table of Contents**

| 1. Objectives                                               |

|-------------------------------------------------------------|

| 2. Parts List                                               |

| 3. Background                                               |

| 3.1. The DEO-Nano FPGA Board                                |

| 3.2. The Nios II Processor                                  |

| 3.3. Design Flow                                            |

| 3.4. Creating a Quartus II Project5                         |

| 3.5. Building the Processor System Using Qsys5              |

| 3.6. Integrate the Qsys System into the Quartus II Project7 |

| 3.7. Compile and Download the Hardware Design               |

| 3.8. Software Development Using Nios II SBT                 |

| 4. Tasks                                                    |

| 4.1. Build and Download the Hardware Design                 |

| 4.2. Build and Download the Software                        |

| 4.3. Discussion                                             |

| 4.4. Bonus Task: Accelerometer                              |

| 5. Grading Sheet                                            |

| Resources                                                   |

# 1. Objectives

In this experiment, you will learn about the hardware of a microcontroller by:

- Building a microcontroller system on an FPGA by integrating Altera's Nios II soft processor and a few peripherals

- Writing software for the FPGA-based microcontroller system

# 2. Parts List

• Altera DE0-Nano FPGA board

• USB A-Type to Mini-B cable

# 3. Background

This experiment involves two main tasks:

1. Building the hardware for a microcontroller system using an FPGA device.

We will use Altera's *DE0-Nano* FPGA development board, which incorporates a small FPGA device and a number of peripherals. To create the microcontroller system, we will configure the FPGA device to implement a soft processor and a number of required components for the processor to function properly.

To configure the FPGA, we will use Altera's *Quartus II* design software. To build the soft processor system, we will use Altera's *Qsys* system integration software to implement a system around Altera's Nios II soft processor core.

2. Developing software to exercise your microcontroller system.

We will use Altera's Eclipse-based *Nios II Embedded Design Suite (EDS)* software development environment to build software for the Nios II-based hardware system.

|   | Intel (Altera) Software                                                                                                                                                                                                                            |

|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | You can obtain and install all the required software for this experiment freely from Altera's website. You will want to download and install <i>Quartus II Web Edition software</i> , which includes Qsys, the Nios II EDS, and Altera IP Library. |

| ſ | Intel acquired Altera in 2015. Altera Quartus II software suite has been renamed to Intel Quartus. Qsys has been renamed to Platform Designer.                                                                                                     |

|   | The free version of Quartus software is now called Intel Quartus Prime Lite Edition.                                                                                                                                                               |

|   | For more details on available Altera software, software licensing, download options, and hardware and software requirements, consult the Intel® FPGA Software Installation and Licensing document.                                                 |

## 3.1. The DE0-Nano FPGA Board

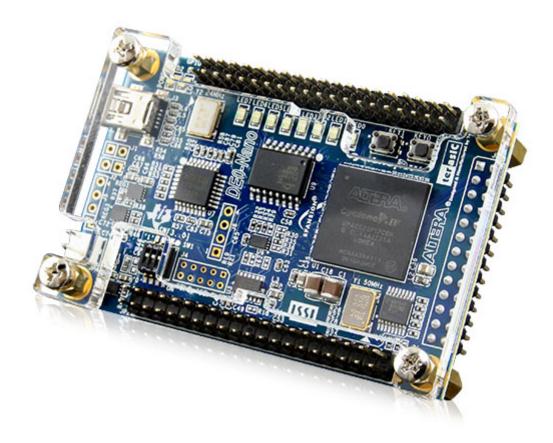

The DE0-Nano is a low-cost, low-power, portable, compact board (49 mm x 75 mm) aimed at developing embedded soft processor systems using the Nios II processor.

Board Features

- Three-axis accelerometer with 13-bit resolution

- Eight-channel, 12-bit resolution analog-to-digital (A/D) converter

- Expansion headers: two 40-pin headers and one 26-pin header

- Two-pin external power header

- 32-MB SDRAM

- 2-Kb EEPROM

- Eight green LEDs

- Four dual in-line package (DIP) switches

- Two push-button switches

#### 3.2. The Nios II Processor

Nios II is a RISC soft processor architecture. A soft processor is a processor that can be implemented on reconfigurable logic, e.g. an FPGA.

Nios II Processor Features

- Full 32-bit instruction set, data path, and address space

- 32 general-purpose registers

- 32 interrupt sources

- External interrupt controller interface for more interrupt sources

- Optional floating-point instructions for single-precision floating-point operations

- Access to a variety of on-chip peripherals, and interfaces to off-chip memories and peripherals

- Hardware-assisted debug module enabling processor start, stop, step, and trace under control of the Nios II software development tools

- Optional memory management unit (MMU) to support operating systems that require MMUs

- Software development environment based on the GNU C/C++ tool chain and the Nios II Software Build Tools (SBT) for Eclipse

The Nios II Processor Reference Handbook states that:

A Nios II processor system is equivalent to a microcontroller or "computer on a chip" that includes a processor and a combination of peripherals and memory on a single chip. A Nios II processor system consists of a Nios II processor core, a set of on-chip peripherals, on-chip memory, and interfaces to off-chip memory, all implemented on a single Altera device. Like a microcontroller family, all Nios II processor systems use a consistent instruction set and programming model.

— Nios II Processor Reference Handbook

$\Omega$

For more information on the Nios II processor, consult its extensive documentation.

### 3.3. Design Flow

Unlike previous experiments, we need to create the hardware of the microcontroller system before we can program it.

In order to create a Nios II soft processor system on the Altera DEO-Nano FPGA board, and write software for it, you are going to use the following software tools:

#### System Builder

used to generate a preconfigured Quartus II project for the DE0-Nano FPGA development board.

#### Quartus II

used to compile all design files, including those generated by Qsys, into an FPGA configuration file, known as an *SRAM Object File* (.sof), which can be downloaded into the FPGA device to implement the designed system.

#### Qsys (Platform Designer)

used to specify the Nios II processor core(s), memory, and other components your system requires. Qsys automatically generates the interconnect logic to integrate the components in the hardware system.

#### Nios II EDS

the Nios II Embedded Design Suite includes Nios II Software Build Tools (SBT) for Eclipse, which is an eclipse installation preconfigured to use a set of plugins to support developing software for the Nios II processor. To create a new Nios II C/C++ application project, the Nios II SBT for Eclipse uses information from the files generated by Qsys to learn about the target hardware.

Here is a summary of the general flow steps; the details will come later

- 1. Use the System Builder utility to generate a Quartus II project preconfigured for the DE0-Nano board. This step is specific to the DE0-Nano board.

- 2. Use Qsys to generate the hardware description of your processor system. In addition to the HDL files, Qsys generates an .sopcinfo file that describes the system.

- 3. Use Quartus II to compile the hardware description generated by Qsys into an FPGA configuration file (.sopcinfo), and to download the configuration file into the FPGA to implement the system's hardware.

- 4. Use Nios II SBT for Eclipse to develop the software for the configured hardware. Nios II SBT for Eclipse learns about the hardware from the Qsys-generated .sopcinfo file, in order to compile the software for the generated hardware.

# 3.4. Creating a Quartus II Project

The Quartus II project will eventually contain all the information required to generate and implement the hardware of our system.

The DE0-Nano kit ships with a convenient software utility called *System Builder*, which creates preconfigured Quartus II projects for the DE0-Nano board. For example, it automatically configures the project for the FPGA device in the DE0-Nano, and configures the pin locations for the selected peripherals.

Run the DE0-Nano's System Builder utility, and choose the following configuration options:

- CLOCK

- LED x 8

Then, press *Generate* to create a Quartus II project. After that, open the generated project in Quartus II by opening the .qpf file. In the next section, we will use Qsys from within this project.

| 0 | Avoid using directories with spaces in their names for your Quartus II or Nios II EDS projects.                                                                                                                                                                     |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |                                                                                                                                                                                                                                                                     |

| A | Since the purpose of this experiment is to understand the makeup of a microcontroller system, it is suggested to create a minimal system by only including the few peripherals listed above. But you are welcome to include any of the other available peripherals. |

|   | For example, the DE0-Nano FPGA board has a built-in accelerometer. You are free to try to use it if you manage to complete the listed tasks in this experiment!                                                                                                     |

|   |                                                                                                                                                                                                                                                                     |

## 3.5. Building the Processor System Using Qsys

Qsys allows you to put together the hardware components that make up your microcontroller system, and to create all the required connections, including the system bus.

We would like to build a Nios II system that includes the following hardware components:

- Nios II/s core with 2 KB of instruction cache

- 20 KB of on-chip memory

- Timer

- JTAG UART

- Eight output-only parallel I/O (PIO) pins

- System ID component

For more information about these and other components, refer to the Embedded Peripherals IP User Guide.

To build this system, run Qsys from the *Tools* menu in Quartus II, and follow the instructions in the Nios II Hardware Development Tutorial, page 1-11 (*Define the System in Qsys* section).

| • | <i>Qsys Errors</i><br>While you are adding the components, connecting them, and configuring them, there will<br>be error messages disappearing gradually till you correctly complete your design. Theses<br>error messages can be useful in reminding you of any missed step.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | <ul> <li><i>Qsys Notes</i></li> <li>1. Edit the export column for the three components: clk_in, clk_in_reset, and external connection.</li> <li>2. Edit the name of the memory component to use a simple short name (e.g. ram).</li> <li>3. After adding the CPU core, use the name of your memory component as Reset Vector memory and exception Vector memory.</li> <li>4. Edit the IRQ numbers in the IRQ column to be 16 for the JTAG UART component, and 1 for the timer.</li> <li>5. Edit the PIO component name to a simple short name that you can remember. You will need it later.</li> <li>6. Generate the base addresses automatically by choosing Assign Base Addresses from the Tools menu in Qsys.</li> <li>7. Finally, use the generate button in Qsys to generate the project files and save them in a known directory.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                         |

| i | <ul> <li><i>Qsys Components</i></li> <li>By following the Nios II Hardware Development Tutorial, you may have some questions about some of the components. Here are some answers for such anticipated questions:</li> <li>1. Although the tutorial asks you to set the cashe size, we don't care about the cache in this experiment. We can use a CPU with no cache. It makes no difference for the purposes of this experiment.</li> <li>2. JTAG UART is used by the development environment to communicate with the microcontroller that we are creating on the FPGA, especially to download and debug software. JTAG is a standard created for this purpose specifically.</li> <li>3. System ID is similarly used by the development tools to identify the target hardware and determine which software to download to which hardware. You can set the target system ID value in the IDE to match the value you may set in the System ID hardware component, in case you use a non-default value.</li> <li>4. Usually, IRQ numbers need to be configured in device drivers or system software. The values set for the JTAG UART and the timer components are the numbers configured in the base system software generated by the Nios II IDE.</li> </ul> |

Your completed Qsys system should look like this:

| Use                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Connections                              | Name                 | Description                 | Export           | Clock  | Base  | End        | IRQ         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|----------------------|-----------------------------|------------------|--------|-------|------------|-------------|

| <ul> <li>Image: A start of the start of</li></ul> |                                          | 🗆 clk_0              | Clock Source                |                  |        |       | 1          |             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | D-                                       | clk_in               | Clock Input                 | clk              |        |       |            |             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | D-                                       | clk_in_reset         | Reset Input                 | reset            |        |       |            |             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | └ `                                      | clk                  | Clock Output                | Click to export  | clk_0  |       |            |             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                          | clk_reset            | Reset Output                | Click to export  |        |       |            |             |

| <b>*</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                          | onchip_mem           | On-Chip Memory (RAM or ROM) |                  |        |       |            |             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | $ \uparrow \rightarrow \rangle$          | clk1                 | Clock Input                 | Click to export  | clk_0  |       |            |             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | $     \longrightarrow$                   | s1                   | Avalon Memory Mapped Slave  | Click to export  | [clk1] |       | 0x0000cfff |             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | $   \downarrow \downarrow \rightarrow$   | reset1               | Reset Input                 | Click to export  | [clk1] |       |            |             |

| <b>Y</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                          | 🗆 cpu                | Nios II Processor           |                  |        |       |            |             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | $ \uparrow+++\rightarrow$                | clk                  | Clock Input                 | Click to export  | clk_0  |       |            |             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ┝┿┼┿                                     | reset_n              | Reset Input                 | Click to export  | [clk]  |       |            |             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ≻+                                       | data_master          | Avalon Memory Mapped Master | Glick to export  | [Clk]  | IRQ ( | ) IRQ 31   | -Υ-         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ≻───≺                                    | instruction_master   | Avalon Memory Mapped Master | Click to export  | [clk]  |       |            |             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ×                                        | jtag_debug_module_re | . Reset Output              | Click to export  | [clk]  |       |            |             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | $      \rightarrow \rightarrow$          | jtag_debug_module    | Avalon Memory Mapped Slave  | Click to export  | [Clk]  |       | 0x00010fff |             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ×—<                                      | custom_instruction_m | Custom Instruction Master   | Glick to export  |        |       |            |             |

| <ul> <li>Image: A set of the set of the</li></ul> |                                          | ⊟ jtag_uart          | JTAG UART                   |                  |        |       |            |             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | $ \uparrow + + \rightarrow \rangle$      | clk                  | Clock Input                 | Click to export  | clk_0  |       |            |             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | $   \uparrow \downarrow \longrightarrow$ | reset                | Reset Input                 | Click to export  | [Clk]  |       |            | ΙL          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | $     \longrightarrow$                   | avalon_jtag_slave    | Avalon Memory Mapped Slave  | Click to export  | [clk]  |       | 0x00011037 | <u>≻</u> 16 |

| <ul> <li>Image: A set of the set of the</li></ul> |                                          | sys_clk_timer        | Interval Timer              |                  |        |       |            |             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                          | clk                  | Clock Input                 | Click to export  | clk_0  |       |            |             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | $   \uparrow + \longrightarrow$          | reset                | Reset Input                 | Glick to export  | [Clk]  |       |            | ΙL          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | $     \searrow$                          | s1                   | Avalon Memory Mapped Slave  | Click to export  | [clk]  |       | 0x0001101f | ┝──IJ       |

| ✓                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                          | sysid                | System ID Peripheral        |                  |        |       |            |             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | $ \uparrow + + \rightarrow$              | clk                  | Clock Input                 | Click to export  | clk_0  |       |            |             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ト+→                                      | reset                | Reset Input                 | Click to export  | [clk]  |       |            |             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                          | control_slave        | Avalon Memory Mapped Slave  | Click to export  | [clk]  |       | 0x0001103f |             |

| <ul> <li>Image: A set of the set of the</li></ul> |                                          | Ied_pio              | PIO (Parallel I/O)          |                  |        |       |            |             |